ニュース

量子トンネルFETを酸化物半導体とSi系材料で実現:LSIの低消費電力化に向けて(2/2 ページ)

東京大学大学院工学研究科教授の高木信一氏らは2017年12月4日、極めて小さな電圧制御で動作可能な量子トンネル電界効果トランジスタを開発したと発表した。

実際にSiおよび、Ge上にZnOを堆積させ、トンネルFETを作製

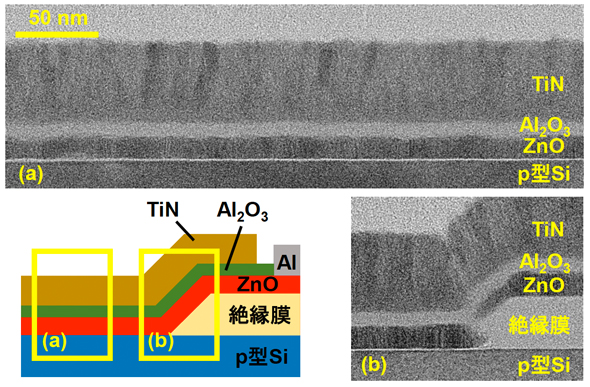

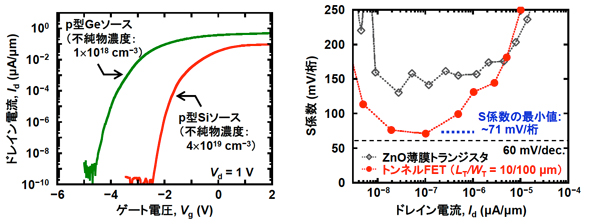

さらに、高木氏らは、高濃度に不純物を添加したSiもしくはGe上に、レーザーアブレーションにより酸化物半導体であるZnO(酸化亜鉛)を堆積することで、トンネルFETを実際に作製した。

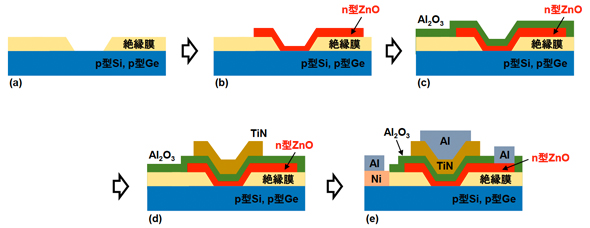

【作製したトンネルFETの製造工程】

(a)高濃度の不純物を添加したp型Siもしくはp型Ge基板上に絶縁膜を堆積し、トンネル接合を形成するためのウィンドウを形成。

(b)酸化物半導体(今回は酸化亜鉛)を全面に堆積し、所望の構造にエッチング。

(c)ゲート絶縁膜としてAl2O3を堆積。

(d)TiNゲート電極を形成。

(e)p型Siもしくはp型Ge上にNiソースコンタクトを、ZnO上にAlドレインコンタクトを形成し、最後に各電極上にAlの引き出し電極を形成。

その結果、「既存の半導体作製プロセスにZnO堆積のみを追加することで、所望の構造を実現可能であることを実証した。オン状態とオフ状態の電流比は8桁を上回り、これまでのトンネルFETと比べて約4倍となった」(東大など)とする。

研究チームでは「今後は、より詳細な材料選択とプロセスの最適化により、さらなるオン電流の増大とS係数の低減を目指す」としている。

なお、本研究は科学技術振興機構(JST)戦略的創造研究推進事業の1つとして実施されたもの。2017年12月3日に国際会議「IEDM 2017」で発行された「Technical Digest」に本研究成果が掲載された。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

分子を用いた縦型共鳴トンネルトランジスタ

分子を用いた縦型共鳴トンネルトランジスタ

物質・材料研究機構(NIMS)らの研究グループは、分子を量子ドットとして用いた縦型共鳴トンネルトランジスターを作製し、その動作を実証することに成功した。 新原理のトランジスタによるLSI動作実証に成功

新原理のトランジスタによるLSI動作実証に成功

産業技術総合研究所は2016年12月5日、新原理のトランジスタ「トンネルFET」を用いたLSIの動作実証に成功したことを明らかにした。 理研ら、酸化亜鉛で異常ホール効果を観測

理研ら、酸化亜鉛で異常ホール効果を観測

理化学研究所(理研)らによる国際共同研究グループは、高品質な酸化亜鉛が磁性伝導電子を持っていることを発見した。低消費電力デバイス用の新たな材料として注目される。 IEDM 2017の全体スケジュールと基調講演

IEDM 2017の全体スケジュールと基調講演

ことしも「IEDM」の季節がやってきた。最先端電子デバイスの研究開発に関する国際学会「IEDM 2017」が、12月に米国で開催される。本シリーズでは、概要と注目の技術講演を紹介していく。 IEDM 2017の技術講演初日、高密度ReRAMと紙基板の2次元トランジスタ

IEDM 2017の技術講演初日、高密度ReRAMと紙基板の2次元トランジスタ

技術講演初日である2017年12月4日から、注目の講演を紹介する。抵抗変化メモリ(ReRAM)や、折り曲げ可能な電子回路(フレキシブルエレクトロニクス)関連で、興味深い講演が多い。 IEDM 2017の講演2日目(12月5日)午後(その2):次世代トランジスタを狙う負性容量FET技術

IEDM 2017の講演2日目(12月5日)午後(その2):次世代トランジスタを狙う負性容量FET技術

12月5日午後の注目講演を紹介する。負性容量トランジスタ、シリコンフォトニクス、非シリコン材料による高耐圧パワーデバイスなどの研究成果が発表される。