ISSCC技術講演の2日目午後ハイライト(その2)、低ジッタの高周波PLL、全天周撮影のカプセル内視鏡など:福田昭のデバイス通信(131) 2月開催予定のISSCC 2018をプレビュー(7)(1/2 ページ)

前回に続き、「ISSCC 2018」2日目午後の技術講演から、見どころを紹介する。低消費電力の2.4GHz帯無線端末用PLL回路や、全天周をVGA解像度で撮影するカプセル内視鏡などが登場する。

低ジッタPLL技術、超高速有線通信技術、ヘルスケア技術を披露へ

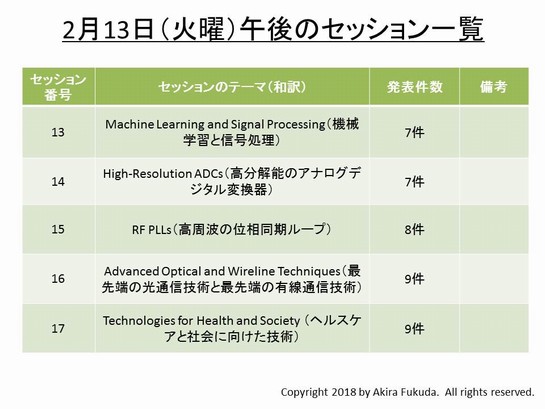

2018年(今年)2月に米国サンフランシスコで開催予定の半導体回路技術に関する国際学会、「ISSCC 2018」の概要をシリーズでお届けしている。前回は、メインイベントである技術講演セッションの2日目午後(現地時間で2月13日火曜日午後1時30分開始予定)から、セッション13〜セッション14のハイライトをお届けした。今回は、セッション15〜セッション17のハイライトをご紹介する。

既に説明したように、2日目の午後に予定されているのは、セッション番号ではセッション13〜セッション17である。すなわち5本の講演セッションが同時並行で進む。セッション名は、「機械学習と信号処理」(セッション13)、「高分解能のアナログデジタル変換器」(セッション14)、「高周波の位相同期ループ」(セッション15)、「最先端の光通信技術と最先端の有線通信技術」(セッション16)、「ヘルスケアと社会に向けた技術」(セッション17)である。

消費電力が0.98mWと低い2.4GHz帯無線端末用PLL回路

セッション15の「高周波の位相同期ループ」では、低消費電力で低ジッタの位相同期ループ(PLL)回路技術の発表が相次ぐ。

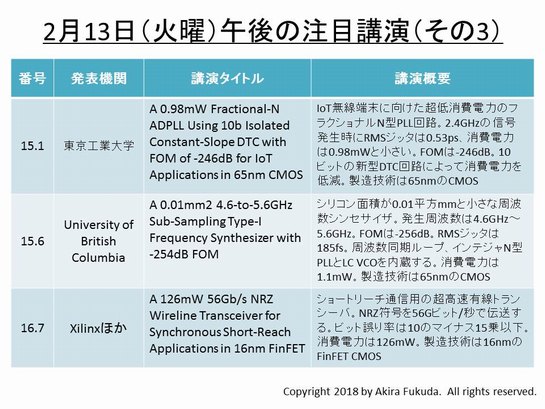

東京工業大学は、IoT(モノのインターネット)の無線端末向けに、消費電力が極めて低いフラクショナルN型PLL回路を発表する(講演番号15.1)。2.4GHzの信号発生時にRMSジッタは0.53ピコ秒(530フェムト秒)と小さく、消費電力は0.98mWと極めて低い。性能指数(FOM)は−246dBである。10ビットの新型DTC(Digital-to-Time Converter)によって消費電力を大幅に低減したとする。製造技術は65nmのCMOSプロセスである。

カナダのUniversity of British Columbiaは、シリコン面積が0.01mm2と狭く、RMSジッタが185フェムト秒と小さい周波数シンセサイザ回路を報告する(講演番号15.6)。信号発生周波数は4.6GHz〜5.6GHz。FOMは-254dBである。オールデジタルの周波数同期ループ回路、インテジャN型PLL回路、LC VCO(Voltage Controlled Oscillator)回路などを内蔵する。消費電力は1.1mW。製造技術は65nmのCMOSである。

セッション16の「最先端の光通信技術と最先端の有線通信技術」では、ショートリーチ(SR: Short Reach)の有線通信に向けた超高速NRZ(Non Return to Zero)トランシーバーが興味深い。

FPGA大手のXilinxと光通信部品メーカーのAcacia Communicationsによる共同研究グループは、NRZ符号のデータを56Gビット/秒と極めて高い速度で伝送するトランシーバー回路を発表する(講演番号16.7)。プリント回路基板上で半導体チップ間を超高速伝送する用途を想定している。ビット誤り率は10のマイナス15乗以下。伝送チャンネルの損失は8dB。送信回路にはデエンファシス機能、受信回路には連続時間線形等化(CTLE: Continuous Time Linear Equalizer)機能を載せた。消費電力は126mW。製造技術は16nmのFinFET CMOSである。

Copyright © ITmedia, Inc. All Rights Reserved.