「RISC-V」はEmbeddedでマーケットシェアを握れるのか:RISC-V Day 2017 Tokyo(1/5 ページ)

2017年12月に開催された「RISC-V Day 2017 Tokyo」から、著者が注目した4つの講演を紹介する。

日本で開催された「RISC-V Day」

やや旧聞になるが、2017年12月に東京大学の本郷キャンパスにある伊藤謝恩ホールで「RISC-V Day 2017 Tokyo」を開催した。この概要は既にレポート「マイコンからHPCまで――RISC-Vが目指す“懐の深さ”」があるのでご存じの方も多いかと思うが、ちょっと違った視点からこの内容を御紹介したいと思う。ちなみに全セッションをご紹介するつもりはなく、筆者の視点から4つほど選んで御紹介したい。

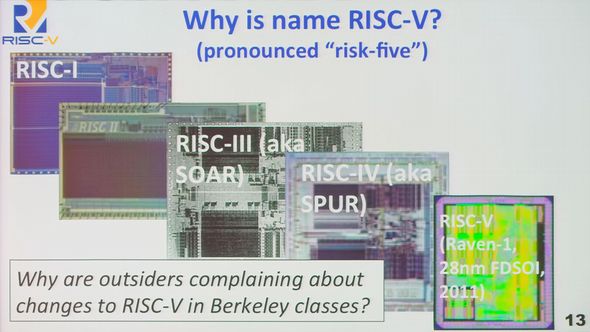

まずはKrste Asanovic教授の公演から。RISC-VはもともとAsanovic教授の研究プロジェクトから生まれたものである。というのは、自由にいじくれる命令セットが必要で、既存の命令セットをベースにしたプロセッサでは命令セットそのものを改変するわけには、いかなかったからだ。まぁこれは当然ではある。このあたりは、前出のレポートの図版にまとめられている通りだ。ちなみになんでRISC-Vかといえば、UC Berkeleyで開発された5番目のRISCプロセッサだから(写真2)だそうである。

ちなみに本来のプロジェクトであるRavenは、どれだけ高い性能および電力効率を実現できるかというもので、Raven-1は26.2GFlops/Wを実現している。Green500の最新の結果(2017年11月)でトップの「菖蒲 System B」ですら、やっと17GFlops/Wを超えたというレベルだから、あくまで研究プロジェクトとはいえ、十分に目的を達した事が分かる。

ここからの展開がちょっと面白い。Asanovic教授によれば、ISAはコンピュータシステムにおいて最も重要なインタフェースだ、とした上で(写真3)、さまざまなコンピュータのコンポーネントのうち、なぜかISAだけは標準もオープンなインプリメントも無い、と主張する(写真4)。また既存のISAも、ビジネスの動向に密接に関係して普及し、そして消えていったとする(写真5)。

左=写真3:いやまぁこれはその通りなのだが、ただこれだけが理由でも無い気もするのだが/中央=写真4:最後の行に主張の全てが込められている気もする/右=写真5:68KとかPowerPCなども入れて欲しかったところではある。ただ、では8051は?とか例外が幾つかあるのも事実(クリックで拡大)

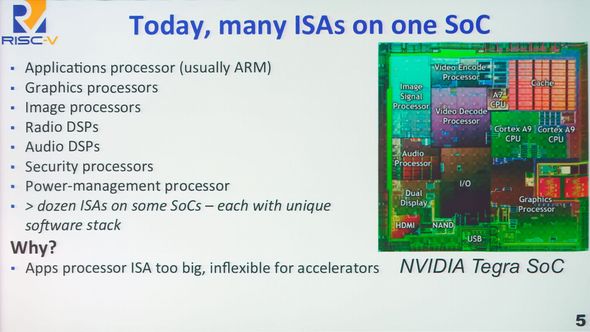

左=写真3:いやまぁこれはその通りなのだが、ただこれだけが理由でも無い気もするのだが/中央=写真4:最後の行に主張の全てが込められている気もする/右=写真5:68KとかPowerPCなども入れて欲しかったところではある。ただ、では8051は?とか例外が幾つかあるのも事実(クリックで拡大)さてAsanovic教授の主張で一番興味深かったのは写真6である。昨今のSoC(System on Chip)はさまざまな機能ブロックが多数盛り込まれているわけだが、こうしたSoCのブロックは全部スクラッチで起こすということはまずなく、あちこちからIP(Intellectual Property)を購入して組み合わせる形なのが普通だ。

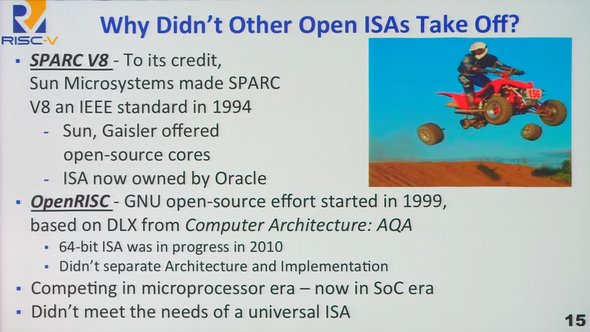

ただ、そうしたIPはそれ自身が当然ながらインテリジェンスな訳で、内部には制御用のプロセッサが普通に含まれる。問題はこうしたプロセッサに使われているISAが全部違っていたりするのが珍しくない(しかもIPベンダー独自のものという事すらある)という話だ。こうしたものはアプリケーションプロセッサというよりはMCUレベルの事も多く、既存のISAでは無駄が多過ぎるとAsanovic教授は指摘する。ちなみにフリーのISAそのものが無かったわけではないが、普及しなかったのはそれなりの理由がある、とする(写真7)。

Copyright © ITmedia, Inc. All Rights Reserved.