「RISC-V」はEmbeddedでマーケットシェアを握れるのか:RISC-V Day 2017 Tokyo(2/5 ページ)

2017年12月に開催された「RISC-V Day 2017 Tokyo」から、著者が注目した4つの講演を紹介する。

「RISC-V」の「命令セット」

さて、話を戻すとそんな訳でもともとはRavenのために開発されたRISC-Vの命令セットであるが、3カ月という短い期間ながら新しいOpen StandardなISAとなるべく設計された、というのはこちらにもある通り。

主要な設計目標は、こちらである。基本はBase+Extensionsという構成で、このBaseをなるべく小さくするとともに変更をやめ(Frozen)、また用途に応じた命令は全部拡張に追いやる、ということで命令セットの一貫性とサポートの容易性を狙っている。そのBase Instructionはこちらにもあるように、RV32E/RV32I/RV64I/RV128Iの4種類である。基本はRV32Eで、

- RV32I:ほとんど同じだが、利用できる汎用レジスタが16個に削減(RV32Iは32個)

- RV64I:RV32Iの64bitアドレス拡張

- RV128I:RV64Iの128bitアドレス拡張

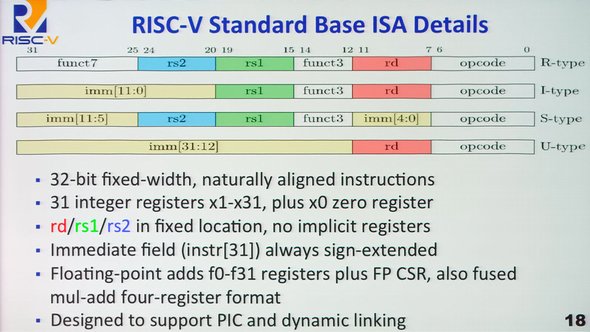

という扱いだ。命令セットのフォーマットは写真8にあるように32bitの固定長で、3オペランド命令にも対応する。例えばadd t0, t1, t2といった具合だ。

ただ面白いというか割り切ったな、という感じなのは、例えばこのadd命令、ISAのレベルではオーバーフローチェックは行わない事になっている。オーバーフローチェックは条件分岐で代替できる(から命令セットではサポートしない)というのがRISC-Vのコンセプトなので、実際にはきちんとadd命令を実行する場合、

add t0, t1, t2

slti t3, t2, 0

slt t4, t0, t1

bne t3, t4, overflow

という4命令を実行してoverflowチェックを行う必要がある。

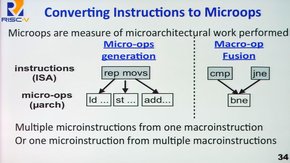

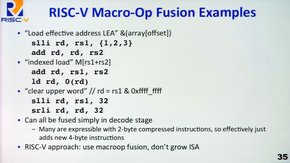

これはどう考えても遅くなりそうなものだが、実はこの辺りもちゃんと抜け道がある。いわゆるMicro-ops Fusion/Macro-Op Fusionの活用だ(写真9)。このケースで言えば、適切な内部アーキテクチャであればこれをMacro-Op Fusionでまとめられる事を前提に(写真10)、「Macro-Opで高速化が可能なものについては命令セットレベルでは何もしない」という割り切りを見せている。

左=写真9:IntelがBanias(Micro-Ops Fusion)やMerom(Macro-Op Fusion)で実装したことで有名になったが、技法そのものはそれ以前から存在している。基本的には内部で一度命令変換を掛けるのが前提/右=写真10:とはいえaddに関しては1つにまとめるのは無理な気もするが(クリックで拡大)

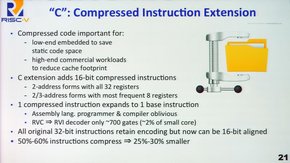

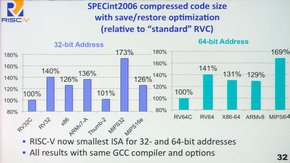

左=写真9:IntelがBanias(Micro-Ops Fusion)やMerom(Macro-Op Fusion)で実装したことで有名になったが、技法そのものはそれ以前から存在している。基本的には内部で一度命令変換を掛けるのが前提/右=写真10:とはいえaddに関しては1つにまとめるのは無理な気もするが(クリックで拡大)ちなみに拡張命令については割愛するが、本稿に関係しそうな一つだけ。Base Instructionに関しては圧縮フォーマットをサポートする(写真11)。これによって命令を16bit Aliginmentで取り込むことが可能で、例えばデコーダーは700ゲート程度で開発できるようになる、とする。この圧縮フォーマットは、Thumb-2とほとんど同程度な程に高効率、とされる(写真12)。

Copyright © ITmedia, Inc. All Rights Reserved.