EUVを適用した小型SRAMセル、imecらが発表:コストはFinFET SRAMと同等に

フラッシュメモリの発明者が率いる新興企業Unisantis Electronics Singapore(以下、Unisantis)が、ベルギーの研究機関imecと共同開発を進めてきた、小型SRAMセルに関する発表を行った。

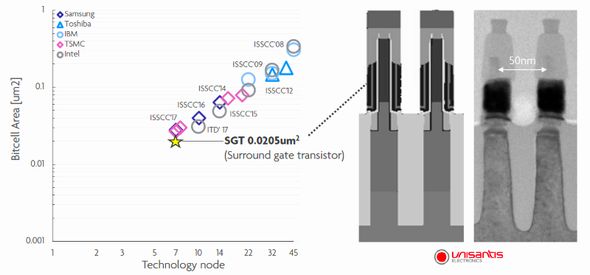

フラッシュメモリの発明者が率いる新興企業Unisantis Electronics Singapore(以下、Unisantis)が、ベルギーの研究機関imecと共同開発を進めてきた、小型SRAMセルに関する発表を行った。この6T-SRAMセルは、面積が0.0184mm2〜0.0205mm2で、Unisantisが未来の最先端チップ向けのビルディングブロックとして開発した、縦型GAA(Gate-All-Around)トランジスタを採用しているという。

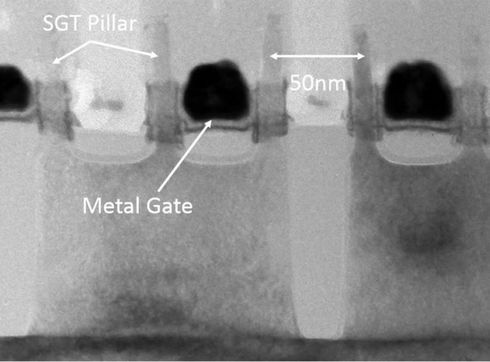

Unisantisとimecの研究チームは、Unisantisが独自開発したSurrounding Gate Transistor(SGT)を採用し、ピラーピッチを50nmまで縮小したという。SGTの設計は、5nmプロセスSRAM向けとしては最適だが、シングルフィンのFinFETの性能を提供するには3つのトランジスタを使用する必要があるため、ロジック向けとしては劣るようだ。

Unisantisの設計は、垂直ナノワイヤとして知られている設計とよく似ている。垂直ナノワイヤは長年にわたり、今後(FinFETの後継)のトランジスタの候補になっている。

これまで、多くの研究者たちが、縦型トランジスタには、商用チップとしての実用化を進める上で妨げとなっている課題があると考えてきた。特にUnisantisの設計の場合、ロジックの分野でFinFETと競争するためには、従来の2〜3倍の高性能化が必要になるとされている。

FinFETに関しては、さらなる微細化を実現できるとされており、2020年には5nmプロセスを適用した量産を開始できる見込みだ。水平方向に積層したGAAトランジスタは、「ナノシート」や「ナノワイヤ」「ナノスラブ」とも呼ばれ、3nmプロセス技術において後継技術になると大いに期待されている。

UnisantisのCTO(最高技術責任者)を務める舛岡富士雄氏は、1980年代に東芝でNAND型フラッシュメモリの開発を手掛けた人物だ。Unisantisは、次世代トランジスタを他に先駆けて開発することにより、いつか未来の半導体の基礎を構築することを目指している。

Samsung Electronicsは2018年2月に、記憶容量が6Tバイト、ビットセル面積が0.026mm2の256MビットSRAMを開発したと発表している。FinFETとEUV(極端紫外線)リソグラフィを使用することで、当時の業界最小となるデバイスを実現した。Samsungは、「テストシリコンを用意したことで、EUVの実用化計画を業界で初めて実現できるという自信を持つことができた」と述べている。

Unisantisは今回、Samsungを大きく上回る小型化を実現しただけでなく、半導体最大手のIntelをも追い抜く成果を達成したと主張する。imecのプレスリリースによると、Unisantisのトランジスタは、EUVを使用して5nmプロセス技術を適用することにより、FinFETプロセスを適用したSRAMと同程度のコストで製造することが可能だという。

【翻訳:田中留美、編集:EE Times Japan】

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

「経験で設計すると失敗する」、ルネサスが提示する16nm FinFET SRAMの課題

「経験で設計すると失敗する」、ルネサスが提示する16nm FinFET SRAMの課題

ルネサス エレクトロニクスは、16nm FinFETプロセスを用いてSRAMを試作したと発表した。プレーナ型MOSFETを使う場合に比べて低い動作電圧で高速読み出しに成功しているが、一方でFinFETと、微細化プロセスを用いたことによる課題も増えている。 CrossbarがMicrosemiにReRAMライセンスを供与

CrossbarがMicrosemiにReRAMライセンスを供与

Microsemiが、ReRAM(抵抗変化メモリ)を手掛けるCrossbarから、ReRAMのライセンス供与を受ける契約を締結した。メモリ業界のアナリストたちは、この契約が、ReRAMの幅広い普及に向けた道を切り開く、重要な触媒として機能するとみているようだ。 微細化限界に達したフラッシュをMRAMで置き換え

微細化限界に達したフラッシュをMRAMで置き換え

埋め込みフラッシュメモリが直面する課題は、微細化の限界である。GLOBALFOUNDRIESは、2xnm以下の技術世代に向けた埋め込み不揮発性メモリとして、MRAM(磁気抵抗メモリ)を考えている。 「MRAMの導入は速く進む」 STTが強気な見解

「MRAMの導入は速く進む」 STTが強気な見解

MRAMを手掛ける数少ない新興企業の1つSpin Transfer Technologies(STT)は、MRAMの根本的な課題を解決する技術の開発を進めているという。CEOに着任したばかりのTom Sparkman氏は、「MRAMの導入は、予想よりもはるかに速く進むのではないか」との見方を示す。 STT-MRAMの基礎――情報の蓄積に磁気を使う

STT-MRAMの基礎――情報の蓄積に磁気を使う

次世代不揮発メモリの候補の1つに、STT-MRAM(スピン注入磁化反転型磁気メモリ)がある。データの読み書きが高速で、書き換え可能回数も多い。今回から始まるシリーズでは、STT-MRAMの基本動作やSTT-MRAが求められている理由を、「IEDM2015」の講演内容に沿って説明していこう。 マイコン大手ルネサスの埋め込みフラッシュメモリ技術

マイコン大手ルネサスの埋め込みフラッシュメモリ技術

今回は、ルネサス エレクトロニクスのマイコン用埋め込みフラッシュメモリ技術「SG(Split Gate)-MONOS(Metal-Oxide-Nitride-Oxide-Silicon)」を解説する。