MRAMのメモリセルと読み書きの原理:福田昭のストレージ通信(105) GFが語る埋め込みメモリと埋め込みMRAM(5)(1/2 ページ)

今回は、MRAMのメモリセルの構造と、データの読み出しと書き込みの原理をご説明する。

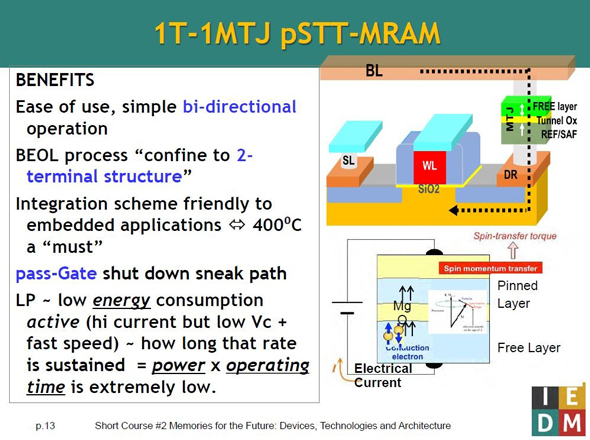

1個のトランジスタと1個の「磁気トンネル接合(MTJ)」でセルを構成

半導体デバイス技術に関する国際会議「IEDM」では、カンファレンスの前日に「ショートコース(Short Course)」と呼ぶ1日間のセミナーを開催している。2017年12月に開催されたIEDMでは、「Memories for the future: device, technologies, and architecture(将来に向けたメモリデバイスの技術とアーキテクチャ)」と題したショートコースが開催された。このショートコースでは6本の技術講座が午前から午後にかけて実施された。

その中から、埋め込みメモリ技術(CMOSロジックとメモリを同じシリコンダイに混載する技術)に関する講座「Embedded MRAM Technology for IoT & Automotive(IoTと自動車に向けた埋め込みMRAM技術)」が興味深かったので、その概要をシリーズでお届けしている。講演者はシリコンファウンダリー(半導体製造請負サービス企業)大手のGLOBALFOUNDRIESでeNVMフェローを務めるDanny P. Shum氏である。

なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

前回は、IoT用および自動車用の埋め込みMRAMに対する要求仕様と、埋め込みメモリにおける書き換え速度と書き換え回数の特性を解説した。今回は、MRAMのメモリセルの構造と、データの読み出しと書き込みの原理をご説明する。

MRAMのメモリセルは通常、1個のセル選択用トランジスタと1個の記憶素子で構成される。セル選択用トランジスタはMOSFETであり、特筆すべきことはあまりない。重要なのは、記憶素子である。記憶素子の特性が、MRAMの特性のほとんどを決めているからだ。

磁気トンネル接合の磁化方向が電気抵抗を大きく変える

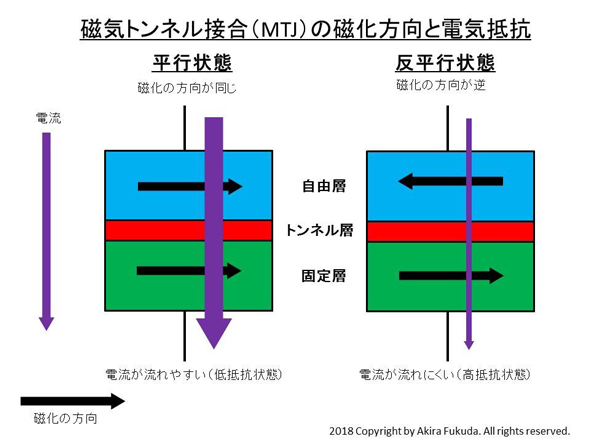

MRAMの記憶素子は「磁気トンネル接合(MTJ:Magnetic Tunneling Junction)」と呼ぶ3層構造の2端子素子を基本とする。3層構造とは、「固定層(Pinned Layer)」、「トンネル層(Tunneling Layer)」、「自由層(Free Layer)」の積層構造を意味する。

固定層とは、磁化(磁気モーメントの方向)が特定の方向に固定されている層である。固定層の材料には、強磁性体を使う。トンネル層とは、電子がトンネル効果(厳密には磁気トンネル効果)によって通過する層である。トンネル層には極薄の絶縁膜を使う。自由層とは、磁化(磁気モーメントの方向)が、固定層の磁化と平行な方向、あるいは反平行な方向のどちらかの状態を取れる層である。自由層の材料には、強磁性体を使う。

MRAMのデータ読み出しでは、磁気トンネル接合の3層構造を貫くように電流を流す。このとき、電気抵抗が高い状態(高抵抗状態)、あるいは、電気抵抗が低い状態(低抵抗状態)のどちらかが出現する。この電気抵抗の違いを、データの違いとして読み出す。

ここで高抵抗状態となるのは、自由層の磁化が固定層とは逆(反平行)に向いているときである。これを磁気トンネル接合では「反平行(AP:AntiParallel)状態」と呼ぶ。そして低抵抗状態となるのは、自由層の磁化が固定層と同じ(平行)になっているときである。これを磁気トンネル接合では「平行(P:Parallel)状態」と呼ぶ。

Copyright © ITmedia, Inc. All Rights Reserved.