連載

埋め込みMRAMのメモリセルと製造プロセス:福田昭のストレージ通信(106) GFが語る埋め込みメモリと埋め込みMRAM(6)(2/2 ページ)

今回は、ロジックへの埋め込みに向けたMRAMのメモリセルと製造プロセスについて解説する。

配線工程の途中でMTJを形成してCMOSロジック互換を維持

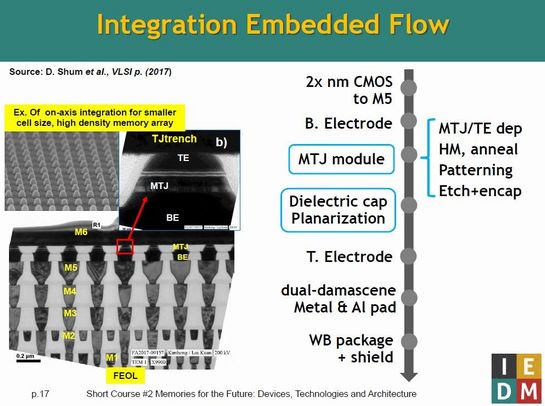

それでは、多層配線の途中で磁気トンネル接合(MTJ)を形成する工程を少し説明しよう。CMOS構造のトランジスタを形成し、多層配線を第5層(M5)まで製造する。ここからMTJの工程が始まる。

始めは、MTJの下層電極(ボトム電極(BE))を形成する。それから磁性層を含めたMTJの製造に入る。磁性層やトンネル絶縁膜層などを成膜し、熱処理とパターニング(リソグラフィとエッチング)を実施する。そしてMTJを保護するキャップ用絶縁膜を成膜し、平坦化を施す。最後に上層電極(トップ電極(TE))を形成する。

その後は、第6層の配線(M6)工程、アルミニウムのパッド形成、ワイヤボンディング、磁気シールド構造を備えたパッケージングへと進む。

埋め込み用MRAMにおける磁気トンネル接合(MTJ)の製造工程。左は磁気トンネル接合(MTJ)の断面を電子顕微鏡で観察した画像と、MTJを形成した多層配線の断面を電子顕微鏡で観察した画像。第5層金属配線(M5)と第6層金属配線(M6)の間にMTJを挿入している。右は磁気トンネル接合(MTJ)を製造する工程のフローチャート。出典:GLOBALFOUNDRIES(クリックで拡大)

(次回に続く)

⇒「福田昭のストレージ通信」連載バックナンバー一覧

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

多層配線工程に記憶素子を埋め込む不揮発性メモリ技術(前編)

多層配線工程に記憶素子を埋め込む不揮発性メモリ技術(前編)

多層配線工程の中に記憶素子を作り込むタイプの埋め込み不揮発性メモリ技術について解説する。 埋め込みMRAM技術がフラッシュとSRAMを置き換えへ

埋め込みMRAM技術がフラッシュとSRAMを置き換えへ

今回は、GLOBALFOUNDRIESが提供する埋め込みMRAMマクロの概要を解説する。 100万回超の書き換えに対応する高信頼次世代NOR

100万回超の書き換えに対応する高信頼次世代NOR

Cypress Semiconductor(サイプレス セミコンダクタ)は2018年6月7日、記者説明会を開催し、2018年5月に発表した車載や産業機器など安全性、信頼性を重視する用途向けの新しいNOR型フラッシュメモリ製品群「Semperフラッシュ ファミリ」の詳細を説明した。 マイコン大手Infineon Technologiesの埋め込みフラッシュメモリ技術

マイコン大手Infineon Technologiesの埋め込みフラッシュメモリ技術

今回は、Infineon Technologiesが開発した埋め込みフラッシュメモリ技術「HS3P(Hot Source Triple Poly)」を取り上げる。HS3Pによるメモリセルトランジスタの動作原理や、どういった分野で実用化されているかを解説する。 書き換え100兆回、遅延ゼロで書き込めるFRAM

書き換え100兆回、遅延ゼロで書き込めるFRAM

Cypress Semiconductor(サイプレス セミコンダクタ)は、車載システムや産業機器、医療機器などのデータ収集用途に向けた不揮発性メモリの新ファミリーを発表した。データの取りこぼしがなく、書き換え回数など耐久性にも優れている。 中国、半導体産業に新たに3兆円を投資

中国、半導体産業に新たに3兆円を投資

中国が、半導体産業に新たに2000億人民元(約3.3兆円)の資金を投じるという。専門家の中には、「中国が技術の後れを取り戻すには、相当の投資が必要になるだろう」との声もある。