2xnm技術で試作した40Mビット埋め込みMRAM(後編):福田昭のストレージ通信(110) GFが語る埋め込みメモリと埋め込みMRAM(10)(2/2 ページ)

2xnm世代のCMOSロジック製造技術によって記憶容量が40Mビット(5Mバイト)の埋め込みMRAMマクロを試作した結果を報告する後編である。ここでは、長期信頼性(書き換えサイクル数とデータ保持期間)とはんだ付け耐熱性に関する試験結果を紹介する。

埋め込みMRAMではんだ付け耐熱性をテストする理由

埋め込みフラッシュメモリでは考慮する必要がなく、埋め込みMRAM(フラッシュ代替用)では懸念される要素に、はんだ付けに対する耐熱性がある。あらかじめプログラムコードを書き込んでから半導体デバイスをプリント基板にはんだ付けすると、200℃を超える高温に半導体デバイスが1分〜3分の間、さらされることになる。

埋め込みフラッシュメモリは、蓄積電荷の活性化エネルギーが大きく、この程度の高温処理ではプログラムコードが失われる恐れはない。しかし埋め込みMRAM(フラッシュ代替用)では高温処理によって、MTJの自由層で磁気モーメントが反転する恐れが出てくる。このため、はんだ付けを想定した高温処理試験により、埋め込みMRAMでデータが不良とならないかどうかを確認しておく必要がある。

埋め込みMRAMでも、SRAM代替用MTJ「スタックA(Stack-A)」はあらかじめデータを書き込んで置くことを想定していない。したがってはんだ付けを想定した高温処理試験を実施すると、大量の不良が発生する。

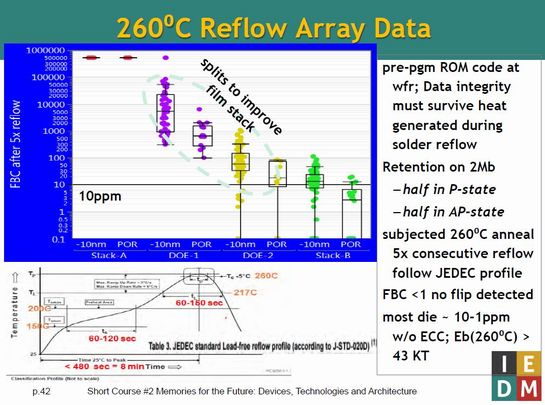

一方、フラッシュメモリ代替用MTJ「スタックB(Stack-B)」を使った埋め込みMRAMでは、はんだ付けを想定した高温処理試験による不良率を低く抑えなければならない。スタックBでは、MTJのエネルギー障壁(Eb)を高くすることなどの工夫で、不良率を低く抑えた。2Mビットのメモリセルアレイで試験を実施した結果、誤り訂正(ECC)回路なしで10ppm〜1ppmとかなり低い不良率を達成した。設計目標である10ppmを満足できている。

はんだ付けを想定した高温処理試験とその結果。左上は、リフローはんだ付けを5回繰り返したときの不良率のグラフ。設計目標となる不良率は10ppmである。左下は、リフローはんだ付け試験の温度プロファイル。217℃を超える時間が60秒から150秒の間で存在し、最高温度は260℃に達する。出典:GLOBALFOUNDRIES(クリックで拡大)

⇒「福田昭のストレージ通信」連載バックナンバー一覧

《次の記事を読む》

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

2xnm技術で試作した40Mビット埋め込みMRAM(前編)

2xnm技術で試作した40Mビット埋め込みMRAM(前編)

2xnm世代のCMOSロジック製造技術によって記憶容量が40Mビット(5Mバイト)の埋め込みMRAMマクロを試作した結果を、前後編で報告する。前編では、高温動作での読み出し電圧マージンの確保と、低温動作での書き込み電圧マージンの維持について紹介する。 埋め込みMRAMのメモリセルと製造プロセス

埋め込みMRAMのメモリセルと製造プロセス

今回は、ロジックへの埋め込みに向けたMRAMのメモリセルと製造プロセスについて解説する。 埋め込みMRAMの磁気トンネル接合(MTJ)に要求される条件

埋め込みMRAMの磁気トンネル接合(MTJ)に要求される条件

多層配線の製造工程に磁気トンネル接合(MTJ)の製造プロセスを組み込むと、どのようなことがMTJに要求されるようになるのか。今回は、その要求を解説する。 半導体メモリのチップとパッケージとシリコンダイ(前編)

半導体メモリのチップとパッケージとシリコンダイ(前編)

「チップ」「デバイス」という単語から想像するイメージは、業界やコミュニティーによってずれがある。では、どのようなずれがあり、なぜ、ずれが生じたのだろうか。 ARMから見た7nm CMOS時代のCPU設計(8)〜消費電力の制約が決めるCPUの「個性」

ARMから見た7nm CMOS時代のCPU設計(8)〜消費電力の制約が決めるCPUの「個性」

今回は、携帯機器などの用途に求められる消費電力の点から、CPUの性能を見てみよう。まず覚えておきたいのは、ゲート長ごとに性能と消費電力のトレードオフが存在するということだ。 半導体シェア、18年1〜3月もSamsungが首位堅持

半導体シェア、18年1〜3月もSamsungが首位堅持

米国の市場調査会社であるIC Insightsは、Samsung Electronicsは2018年第1四半期(1〜3月)の半導体売上高で、Intelを抑え首位を堅持したと発表した。メモリ市場の成長が続いていることが影響したと考えられる。