垂直方向に並んだセルトランジスタを一気に作る:福田昭のストレージ通信(123) 3D NANDのスケーリング(11)(1/2 ページ)

3D NANDフラッシュ製造におけるキープロセスの1つ、「メモリセルの形成(Cell Formation)」技術について解説する。

3D NANDフラッシュにおけるセルトランジスタの構造

半導体メモリ技術に関する国際会議「IMW(International Memory Workshop)」では、カンファレンスの前日に「ショートコース(Short Course)」と呼ぶ1日間のセミナーを開催している。今年(2018年)5月に開催されたIMWのショートコースでは、9件の技術講座(チュートリアル)が午前から午後にかけて実施された。その中から、3D NANDフラッシュメモリ技術に関する講座「Materials, Processes, Equipment Perspectives of 3D NAND Technology and Its Scaling(3D NAND技術とそのスケーリングに関する材料とプロセス、製造装置の展望)」がとても参考になったので、その概要をシリーズでお届けしている。講演者は半導体製造装置の大手ベンダーApplied MaterialsのSean Kang氏である。

なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

前回と前々回は、3D NANDフラッシュ製造における重要技術(キープロセス)の1つである「高アスペクト比(HAR:High Aspect Ratio)のパターン形成」技術を解説した。今回は、同じくキープロセスの1つである、「メモリセルの形成(Cell Formation)」技術をご紹介する。

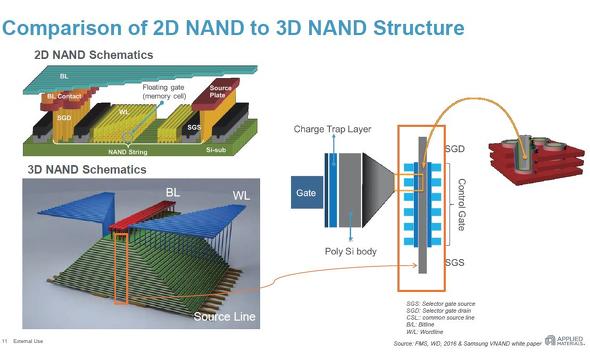

本シリーズの第3回「2D NANDフラッシュと3D NANDフラッシュのセルアレイ構造」でご説明したように、3D NANDフラッシュメモリでは、メモリセルの連なりであるセルストリングが垂直方向に伸びている。データを記憶するメモリセルは、独自構造のトランジスタであり、セルトランジスタとも呼ばれる。

セルトランジスタは、制御ゲート(ワード線)とゲート絶縁膜、多結晶シリコンのチャンネルで構成される。ゲート絶縁膜はシリコン酸化膜とシリコン窒化膜、シリコン酸化膜の3層構造(最後のシリコン酸化膜を省いた2層構造のこともある)となっており、シリコン窒化膜に意図的に形成した欠陥(電荷捕獲(チャージトラップ)準位)に電子をチャンネルから飛び込ませることで、セルトランジスタのしきい電圧を制御する。しきい電圧の違いが、セルトランジスタに記憶する論理値の違いに対応する。例えば3ビット/セル(TLC)方式の3D NANDフラッシュメモリでは、セルトランジスタに8通りのしきい電圧を与える。

Copyright © ITmedia, Inc. All Rights Reserved.