連載

垂直方向に並んだセルトランジスタを一気に作る:福田昭のストレージ通信(123) 3D NANDのスケーリング(11)(2/2 ページ)

3D NANDフラッシュ製造におけるキープロセスの1つ、「メモリセルの形成(Cell Formation)」技術について解説する。

マルチペア薄膜の堆積とHARエッチングによる孔開けが準備段階

本シリーズの第7回で述べたマルチペア薄膜の形成工程と、第10回で述べたメモリスルーホールの形成工程はいずれも、セルトランジスタのストリングを製造する準備段階に相当する。マルチペア薄膜は、制御ゲート膜と素子分離膜(隣接するセルトランジスタを電気的に分離する膜)である。メモリスルーホールは、セルストリング全てのチャンネルとゲート絶縁膜を一気に形成するために、必要な細長い孔である。

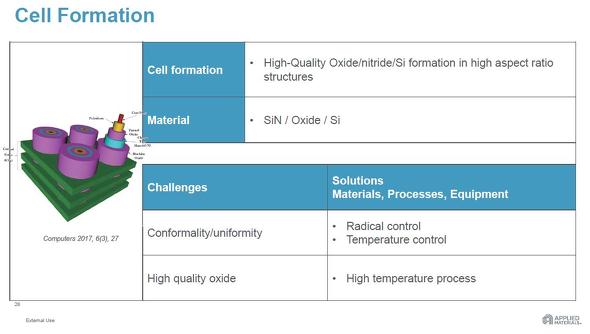

メモリスルーホールの側壁にはまず、ゲート絶縁膜を形成する。3層構造あるいは2層構造の絶縁膜を細くて深い孔の側壁に、均一に成膜しなければならない。非常に難しい技術である。そしてメモリスルーホールの細くて深い孔を多結晶シリコンによって埋め込む。これも同様に、非常に難しい技術である。いずれも非常に難しい技術なのだが、数多くのセルトランジスタを一気に作れるという、大きなメリットがある。上手く作れさえすれば、スループットを大幅に高められる。

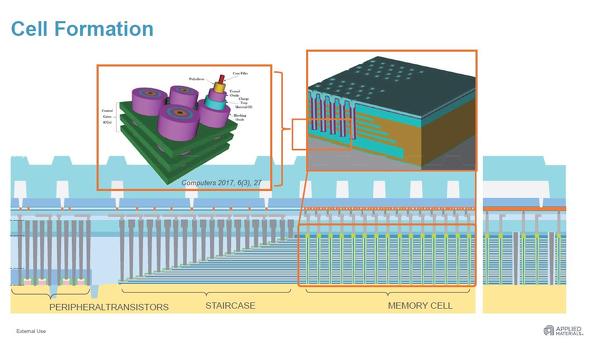

3D NANDフラッシュメモリの断面構造図と、「メモリセルの形成(Cell Formation)」部分(橙色の実線で囲んだ部分、上方は拡大図)。出典:Applied Materials(クリックで拡大)

「メモリセルの形成(Cell Formation)」技術における課題と解決策のまとめ。左の図はセルストリングの一部を拡大したもの。緑色の板が制御ゲート、紫色の円筒がシリコン酸化膜、水色の円筒がシリコン窒化膜(電荷捕獲層)、橙色の円筒が多結晶シリコンのチャンネル、赤色の柱がコアフィラー。出典:Applied Materials(クリックで拡大)

(次回へ続く)

⇒「福田昭のストレージ通信」連載バックナンバー一覧

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

膨張を続けるデジタルデータをNANDフラッシュが貯蔵

膨張を続けるデジタルデータをNANDフラッシュが貯蔵

2018年5月に開催された「IMW(International Memory Workshop)」のショートコースで行われた技術講座から、「Materials, Processes, Equipment Perspectives of 3D NAND Technology and Its Scaling(3D NAND技術とそのスケーリングに関する材料とプロセス、製造装置の展望)」の概要をシリーズでお届けする。 メモリセルアレイのベースとなるマルチペア薄膜の形成

メモリセルアレイのベースとなるマルチペア薄膜の形成

3D NANDフラッシュメモリの製造プロセスにおける重要な技術の一つであるマルチペア(Multi-pair)薄膜の成膜(Deposition)」を解説する。 高アスペクト比の細長い孔をハードマスクによって形成

高アスペクト比の細長い孔をハードマスクによって形成

3D NANDフラッシュ製造における重要技術の一つである、「高アスペクト比(HAR:High Aspect Ratio)のパターン形成」技術について解説する。 高アスペクト比の細長い孔をハードマスクによって形成(続き)

高アスペクト比の細長い孔をハードマスクによって形成(続き)

前回に続き、3D NANDフラッシュ製造におけるキープロセスの1つ、「高アスペクト比(HAR:High Aspect Ratio)のパターン形成」を取り上げる。今回は、同技術の異方性エッチングについて解説する。 CypressとSK Hynix System ICが合弁事業

CypressとSK Hynix System ICが合弁事業

Cypress Semiconductorは、SK Hynix System ICとNANDフラッシュメモリの合弁事業を始める。合弁会社は本社を香港に置き、SK Hynix System ICが60%、Cypressが40%の株式を保有する。 DRAMの価格下落が加速

DRAMの価格下落が加速

メモリチップ価格の追跡を手掛ける市場調査会社TrendForceによると、DRAM価格は2018年第4四半期(10〜12月)に同年前期比で約5%下落する見込みだという。