Intelが新しい3D積層チップ技術「Foveros」を発表:ヘテロ統合への第一歩を踏み出す

Intelは、新しい3Dパッケージング技術「Foveros」のデモを披露した。2019年後半には提供できる見込みだという。Intelは、このFoverosの開発に20年間を費やし、ロジックとメモリを組み合わせた3D(3次元)のヘテロジニアス構造でダイ積層を実現した。

Intelは、新しい3Dパッケージング技術「Foveros」のデモを披露した。2019年後半には提供できる見込みだという。同社のチーフアーキテクト兼コア/ビジュアルコンピューティンググループ担当シニアバイスプレジデントを務めるRaja Koduri氏は、2018年12月12日(米国時間)に開催されたイベント「Architecture Day」において、将来のコンピューティングアーキテクチャに関する展望について説明した他、新しいプロセッサマイクロアーキテクチャとグラフィックスアーキテクチャも発表した。

Intelは、このFoverosの開発に20年間を費やし、ロジックとメモリを組み合わせた3D(3次元)のヘテロジニアス構造でダイ積層を実現した。Foverosは、3Dパッケージングの概念を、CPUやグラフィックス、AI(人工知能)向けプロセッサなどの高性能ロジックにも拡大しているという点で、現在利用可能なパッシブインターポーザーや積層メモリ技術とは異なる。

Koduri氏は、「われわれは現在、プロセス技術や高性能パッケージングの分野におけるリーダーシップを強化しているところだ」と述べる。

同氏は、「半導体業界は、さまざまな種類の半導体チップとチップレットを、統合型3Dパッケージとして接続することを追求してきた。これを受け、当社はついに、実際に製造可能な製品として実現する方法を見つけ出すことができた」と述べている。

またKoduri氏は、「Intelは既に、顧客企業からの要望に応じ、Foveros技術を適用した製品を製造している」と述べる。同氏はイベント会場において、ハイブリッド型のx86アーキテクチャを披露した。12×12×1mmのFoverosパッケージ上に、10nmプロセスのロジックチップレットと22nmプロセスベースのダイ、メモリを搭載したもので、待機電力はわずか2mWだという。

同氏は、「Foveros技術は、柔軟性に優れるため、新しいフォームファクタの中で、IP(Intellectual Property)ブロックを各種メモリやI/Oと調和させたり適合させたりすることが可能になる。Intelはこの技術を、当社の全ての製品シリーズに適用する予定だ」と述べている。

Koduri氏は、Foverosを発表した際、2時間に及ぶプレゼンテーションを行い、コンピューティングのパラダイムが劇的に変化し、いわゆる「ムーアの法則」が行き詰まりを見せている時代における、Intelのアーキテクチャロードマップのビジョンについて説明した。

同氏は、「コンピューティング時代は今後、アーキテクチャによって定義されるのではないだろうか」と予測する。今後10年の間に、コンピューティングアーキテクチャの分野にさらなるイノベーションが生まれ、過去50年間に起きたイノベーションの数を上回るだろう」と語った。

「われわれはこうした時代に、自ら道を切り開いていくつもりだ」(同氏)

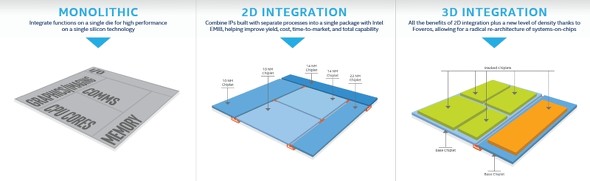

Intelは「2Dと3Dのパッケージング技術を持っていることで、より小さなチップレットを組み合わせるという柔軟性を実現できるので、さまざまなアプリケーションに適用できる」と述べる 出典:Intel(クリックで拡大)

【翻訳:田中留美、編集:EE Times Japan】

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

Intel 10nmプロセスの遅れが引き起こしたメモリ不況

Intel 10nmプロセスの遅れが引き起こしたメモリ不況

2018年、メモリ市場の成長に暗雲が立ち込め、メモリ不況が避けられない事態となった。アナリストらは、メモリの過剰供給による価格の下落を要因として指摘しているが、どうも腑に落ちない。そこで筆者は、Intelの10nmプロセスの遅れという点から、メモリ不況の要因を探ることにした。 2.5D(2.5次元)の新世代パッケージング技術

2.5D(2.5次元)の新世代パッケージング技術

TSMCが開発した2.5次元のパッケージング技術「CoWoS(Chip on Wafer on Substrate)」と「InFO(Integrated Fan-Out wafer level packaging)」を解説する。CoWoSでは、「シリコンインターポーザ」の導入により、樹脂基板では困難な微細配線が可能になった。InFOは、樹脂基板とバンプを省いたことで、低コストで高密度な再配線構造を形成できるようになり、パッケージの小型化と薄型化を実現した。 3次元集積化(3D IC)の理想と現実

3次元集積化(3D IC)の理想と現実

今回は、なぜシステムを複数のチップに分ける必要があるのかを説明する。後半では、パッケージに求められる目標を達成する“究極のパッケージング技術”として期待されたシリコン貫通ビア(TSV: Through Silicon Via)と、旧世代のパッケージング技術との間に存在する、大きなギャップについて解説したい。 2018年半導体売上高1位はSamsungか、Intelとの差が開く

2018年半導体売上高1位はSamsungか、Intelとの差が開く

2018年の半導体売上高ランキングでは、Samsung ElectronicsがIntelとの差をさらに広げ、2017年に続き首位に立つ見込みだという。市場調査会社のIC Insightsが発表した。 EUVプロセス開発、けん引役をTSMCに譲ったIntel

EUVプロセス開発、けん引役をTSMCに譲ったIntel

技術開発をリードするごくわずかな半導体メーカーは、2019年にはEUV(極紫外線)リソグラフィによって、半導体のトランジスタ密度がその物理的限界にさらに一歩近づくと断言している。かつて世界最大の半導体メーカーだったIntelは、EUVで先頭に立とうとすることを諦めたようだ。 Intel、“組み込みAIチップ”のPC搭載を狙う

Intel、“組み込みAIチップ”のPC搭載を狙う

Intelは、CPUの他に、Movidiusが手掛けてきたVPU(Vision Processing Unit)のような推論チップを、PCに搭載することを目指しているようだ。