車載向けSoC、高速かつ低電力で深層学習を実行:DNNアクセラレーターを実装

東芝デバイス&ストレージは、深層学習を用いた画像認識を高速かつ低消費電力で実行できる車載向けSoCを開発した。

従来SoCに比べて処理速度は約10倍、電力効率は約4倍

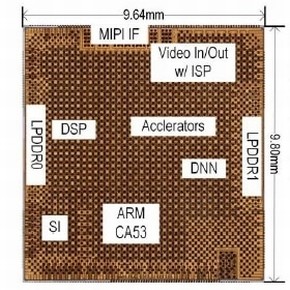

東芝デバイス&ストレージは2019年2月、深層学習を用いた画像認識を高速かつ低消費電力で実行できる車載向けSoCを開発したと発表した。従来のSoCに比べて処理速度は約10倍、電力効率は約4倍である。自動車向け機能安全規格「ISO 26262」にも対応している。

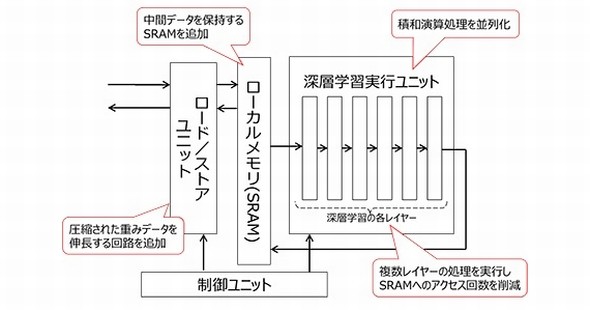

開発したSoCは、深層学習による画像認識をハードウェア上で実行するためのDNNアクセラレーターを実装した。このDNNアクセラレーターには大きく3つの特長があるという。その1つは「積和演算プロセスを並列化した」ことである。256個の積和演算ユニットを搭載したプロセッサを4個内蔵した。これによって、画像認識の処理性能を高めた。

2つ目は、「DRAMへのアクセスで消費される電力を低減した」ことである。開発したSoCは、演算プロセスの中間データを保持するための専用SRAMを、実行ユニットの近くに配置した。この専用SRAMに収まるよう、深層学習の推論処理を分割することで、DRAMへのアクセス回数を削減できるという。また、重みデータを事前に圧縮して保存し、読み込む時にそのデータを伸長する回路を実装した。これによって、重みデータの読み込みに用いるデータ量を減らすことができた。

3つ目は、「SRAMへのアクセスで生じる消費電力の節減」である。開発したSoCは、深層学習の推論処理を行う各レイヤーをパイプライン接続した。このため、1回のSRAM参照で複数レイヤーの処理を実行することが可能となり、消費電力を削減した。これまでのように、各レイヤーで処理が終わるたびにSRAMを参照しなくても済むという。

同社は今後、精度の向上や消費電力のさらなる低減を行い、2019年9月には車載向け画像認識AIプロセッサ「Visconti 5」として、サンプル出荷を始める予定だ。

なお、今回の研究成果は、半導体集積回路技術の国際会議「ISSCC(International Solid-State Circuits Conference) 2019」(2019年2月17〜21日、米国カリフォルニア州サンフランシスコ)で、その詳細を発表した。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

東芝、SSD向けにPAM4採用のブリッジチップ開発

東芝、SSD向けにPAM4採用のブリッジチップ開発

東芝は、SSD(Solid State Drive)内に組み込まれるフラッシュメモリとコントローラICの間に挿入するブリッジチップを開発した。SSDにおいて高速化と大容量化の両立を可能にする技術である。 東芝、パワー半導体向け駆動回路を新たに開発

東芝、パワー半導体向け駆動回路を新たに開発

東芝は、モーター駆動用のパワー半導体を高い効率でスイッチングするための駆動回路を開発した。 日立、CMOSアニーリングマシンを名刺形状で実現

日立、CMOSアニーリングマシンを名刺形状で実現

日立製作所は、従来型コンピュータに比べて処理性能を約2万倍、エネルギー効率を約17万倍に高めた名刺サイズのCMOSアニーリングマシンを開発した。 東工大、極低消費電力のデジタルPLLを開発

東工大、極低消費電力のデジタルPLLを開発

東京工業大学は、消費電力が極めて小さい分数分周タイプのデジタル位相同期回路(PLL)を開発した。従来の開発品に比べて消費電力を60%削減できるという。 広島大学ら、300GHz帯トランシーバーICを開発

広島大学ら、300GHz帯トランシーバーICを開発

広島大学、情報通信研究機構(NICT)、パナソニックは、シリコンCMOS回路を用いた300GHz帯ワンチップトランシーバーICを共同開発した。80Gビット/秒のデータ伝送が可能となる。 ISSCC 2019の目玉はAIと5Gに、CPUの話題は少ない?

ISSCC 2019の目玉はAIと5Gに、CPUの話題は少ない?

2019年2月17〜21日に米国カリフォルニア州サンフランシスコで開催される半導体回路技術関連の国際学会「ISSCC 2019」は、発表内容のほとんどが、機械学習(マシンラーニング)や高速ネットワーク、メモリが主役となる“データ時代”に関するものとなりそうだ。