ニュース

表面欠陥密度を半減させたSiCエピウエハーを開発:昭和電工

昭和電工は2019年8月、パワー半導体用SiC(炭化ケイ素)エピタキシャルウエハーとして、既に量産中の6インチサイズの低欠陥グレード品をさらに高品質化した第2世代製品を開発したと発表した。

昭和電工は2019年8月、パワー半導体用SiC(炭化ケイ素)エピタキシャルウエハーとして、既に量産中の6インチサイズの低欠陥グレード「ハイグレードエピ」(以下、HGE)をさらに高品質化した第2世代製品(以下、HGE-2G)を開発したと発表した。

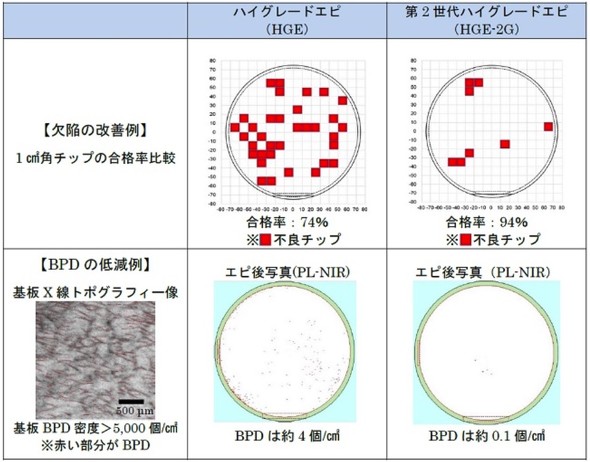

開発したHGE-2Gは、エピタキシャル成長プロセスの高度化などにより、デバイス初期歩留りに影響する表面欠陥密度を従来のHGEの2分の1以下に抑えた。同時に、デバイスの信頼性(通電劣化)に影響する基底面転位の基板からの伝播における変換効率を従来の10倍以上にまで高めたとする。

昭和電工は開発したHGE-2Gを、100A級の大電流を扱う電気自動車や鉄道車両向けのモーター駆動インバーターモジューに搭載するチップサイズが10mm角程度に及ぶ大型のSiC-MOSFETチップなどに向ける方針。

同社は、「SiCエピタキシャルウェハーの世界需要は、2025年に1500億円規模に拡大すると予想されている。当社は、世界最大の外販メーカーとして、急拡大する市場に対し、高信頼性品の開発や積極的な増産投資を通じ、SiCデバイスの普及に貢献するとともに、(収益性と安定性を高レベルで維持できる)個性派事業への成長を図る」としている。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

昭和電工が高品質SiCウエハーを増産、月産9000枚へ

昭和電工が高品質SiCウエハーを増産、月産9000枚へ

昭和電工は2018年7月3日、SiC(炭化ケイ素)エピタキシャルウエハー(以下、エピウエハー)の高品質グレード品である同社製品「ハイグレードエピ」について、増産を決定したと発表した。 車載インバーターのSiC採用、2021年以降に活発化

車載インバーターのSiC採用、2021年以降に活発化

ドイツ・ニュルンベルクで毎年5月ないし6月に開催されるパワーエレクトロニクスの展示会「PCIM Europe」において、年々存在感が高まっているのが、電気自動車(EV)やプラグインハイブリッド自動車(PHEV)向けのパワーエレクトロニクス技術の紹介に特化したブース「E-Mobility Area」である。 Siの限界を突破する! 3300V IGBTの5Vゲート駆動に成功

Siの限界を突破する! 3300V IGBTの5Vゲート駆動に成功

2019年5月、東京大学生産技術研究所の更屋拓哉助手、平本俊郎教授を中心とする研究グループは、耐圧3300VクラスのシリコンによるIGBT(絶縁ゲート型バイポーラトランジスタ)を、ゲート駆動電圧5Vで動作させることに成功したと発表。2019年5月28日に、東京都内で記者会見を開催し、開発技術の詳細を説明した。 主流はシリコンパワー半導体、EV市場に期待大

主流はシリコンパワー半導体、EV市場に期待大

東芝デバイス&ストレージは、2019年4月、東京都内でパワー半導体に関する技術説明会を実施し、パワー半導体の市場予測や東芝のパワー半導体事業の現状などを説明した。東芝デバイス&ストレージでパワーデバイス技師長を務める川野友広氏は、現在の主流はシリコン製品であり、特に高性能が要求されるMOSFETとハイパワー製品(=IGBT)に注力するとしつつ、SiC(炭化ケイ素)パワーデバイスの将来性にも触れ、「パワー半導体事業は非常に安定した事業だ。今後も製品開発と投資を継続していく」と語った。 三菱電機、SiCパワー半導体製品を用途別に提案

三菱電機、SiCパワー半導体製品を用途別に提案

三菱電機は、「TECHNO-FRONTIER 2019(テクノフロンティア)」で、パワーエレクトロニクス機器の省エネ化につながる、SiC(炭化ケイ素)パワー半導体/モジュール製品を一堂に展示した。 STがSiCウエハーメーカーNorstelを買収

STがSiCウエハーメーカーNorstelを買収

STMicroelectronics(以下、ST)は2019年2月6日(スイス時間)、スウェーデンのSiC(炭化ケイ素)ウエハーメーカーであるNorstelの株式を過半数取得すると発表した。