1個のパッケージでシステムを実現するSiP:福田昭のデバイス通信(214) 2019年度版実装技術ロードマップ(25)(2/2 ページ)

今回は、SiP(System in Package)を実現する幾つかの手法のうち、2.X次元(2.XD)の実装技術を解説する。ここでカギとなるのは、インタポーザだ。

インターポーザとビルドアップ基板が2.XD実装のカギ

SiPで実装密度が最も高くなるのは、複数のシリコンダイを積層してシリコン貫通ビア(TSV: Through Silicon Via)でシリコンダイ同士を接続する、3D積層のSiPだろう。しかしTSVを使った3D積層には製造コストが高い、積層するシリコンダイの寸法に制限がある、放熱性が低い、といった課題があり、一部の用途を除いては実用化されていない。代わりに開発されているのが、2.X次元(2.XD)の実装技術によるSiPである。さまざまな構造が提案され、実用化されている。

2.XD実装のカギとなる要素技術は、ビルドアップ基板とインターポーザである。シリコンダイの入出力パッドは微細なピッチでレイアウトされているので、そのままではプリント基板に接続できない。そこでシリコンダイの入出力パッドにインターポーザを接続し、インターポーザ内部で配線ピッチを広げる。このためインターポーザのことを「再配置配線層(RDL:Re-Distribution Layer)」と呼ぶことが多い。

インターポーザで配線ピッチを広げたとしても、あまり広くしてはSiPが巨大化してしまう。そこで微細な配線が可能なビルドアップ基板でインターポーザと接続する。インターポーザの表面(シリコンダイ側)と裏面(ビルドアップ基板側)は貫通電極によって結ぶ。

シリコンダイはインターポーザの上に横に並べる。積層構造に比べると実装密度は下がるものの、シリコンダイの間隔を狭めることで、実装密度をなるべく高めようとしている。シリコンダイとインターポーザの間は、はんだバンプで接続(フリップチップ接続)する。インターポーザとビルドアップ基板の間もはんだバンプで接続することが多い。シリコンダイとインターポーザの間および、インターポーザとビルドアップ基板の間には、樹脂(アンダーフィル樹脂)を注入して信頼性を確保する。

インターポーザの標準的な材料はシリコン(Si)である。シリコンインターポーザが有利な点は、シリコン半導体の微細加工技術によって微細で高密度な配線を形成できることだ。不利な点は、単位面積当たりのコストがプリント基板に比べるとはるかに高いことである。インターポーザが大きくなると、製造コストが大幅に増加する。

そこで製造コストを下げるために、シリコンインターポーザでも貫通電極(TSV)を使わずにシリコン上に形成したRDLだけでシリコンダイとビルドアップ基板を接続する構造や、ビルドアップ基板の表面に微細配線層を形成してシリコンダイを直接接続することでインターポーザを不要にした構造などが提案されている。

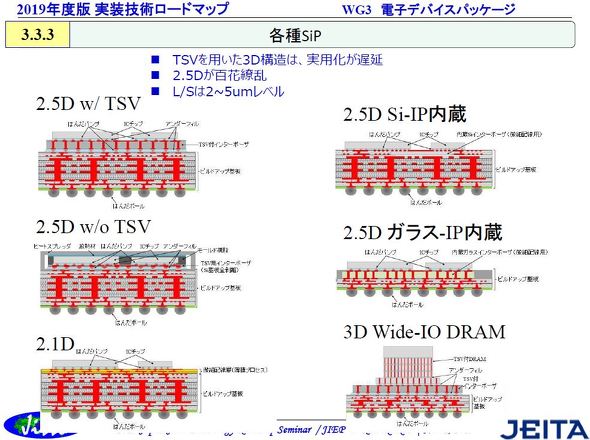

2.XD実装技術や3D実装技術などを駆使したSiP(シリコンインパッケージ)の例。左上はシリコンインターポーザにTSVを形成した構造。左中央はRDLだけをインターポーザとした構造。信頼性を維持するためにシリコンダイをモールド樹脂で、RDLをヒートスプレッダで封止している。左下はビルドアップ基板の表面に微細配線層を薄膜プロセスで形成してインターポーザを不要にした構造。右上はビルドアップ基板の最上部にシリコンの小片を埋め込んで隣接するシリコンダイ同士を接続した構造。右中央はガラス基板に貫通電極を形成してインターポーザとした構造。右下はDRAMチップをTSVによって積層したモジュールを、TSV付きインターポーザに搭載した構造である。出典:JEITA(クリックで拡大)

(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

パッケージの多端子化と小型化、薄型化、低コスト化が進む

パッケージの多端子化と小型化、薄型化、低コスト化が進む

今回は第3章「電子デバイスパッケージ」から、各種パッケージの技術動向を紹介する。半導体パッケージの歴史は、多端子化と小型化、薄型化、低コスト化の歴史でもある。 IoT社会に向けて多様化する電子デバイスパッケージ

IoT社会に向けて多様化する電子デバイスパッケージ

今回から、第3章「電子デバイスパッケージ」の概要を説明していく。「2019年度版 実装技術ロードマップ」で約70ページが割かれている重要な章だ。序章では、年間で1兆個のセンサーが生産される「トリリオンセンサー」について言及している。【訂正あり】 第5世代(5G)移動通信システムへの移行と課題

第5世代(5G)移動通信システムへの移行と課題

前回に続き、「第5世代(5G)移動通信システム」の内容を紹介するシリーズ。今回は、4G(第4世代)から5Gへの移行シナリオについて説明する。 TSMCがEUV適用7nmプロセスを商用化

TSMCがEUV適用7nmプロセスを商用化

世界最大のファウンドリーであるTSMCは2019年10月7日(台湾時間)、「業界で初めてEUV技術を商用化」(同社)し、EUVを採用した7nmプロセス「N7+」を発表した。同社は報道向け発表資料の中で、「当社は現在、複数の顧客企業からのN7+プロセスへの需要に対応すべく、生産能力を迅速に拡大しているところだ」と述べている。 半導体メーカーの働き方改革 〜半導体技術者の在宅勤務は可能か?

半導体メーカーの働き方改革 〜半導体技術者の在宅勤務は可能か?

今回は、いつもとは毛色を変えて、“半導体メーカーの働き方改革”に目を向けてみたい。筆者がメーカー勤務だった時代と現在とでは、働き方にどのような違いがあるのだろうか。 パナと日本IBMが半導体製造装置分野で協業

パナと日本IBMが半導体製造装置分野で協業

パナソニックと日本IBMが、半導体製造装置分野で協業する。パナソニックが製造、販売するプラズマダイサーなどの半導体後工程製造装置の価値を高めるソフトウェアなどをパナソニックと日本IBMで共同開発し、パナソニックが製造装置ともに提供する。