連載

部品内蔵基板の組み立て技術:福田昭のデバイス通信(219) 2019年度版実装技術ロードマップ(30)(1/3 ページ)

今回は、部品内蔵基板の組み立て工程を紹介する。半導体チップをフェースダウン(回路面を下にした状態)で基板に搭載する技術、フェースアップ(回路面を上にした状態)で基板に搭載する技術、微細な配線を形成できる技術の3つについて解説したい。

実装面積削減と高速化に寄与する部品内蔵基板

電子情報技術産業協会(JEITA)が発行した「2019年度版 実装技術ロードマップ」に関する完成報告会(2019年6月4日に東京で開催)と同ロードマップの概要をシリーズでご報告している。今回はその第30回である。

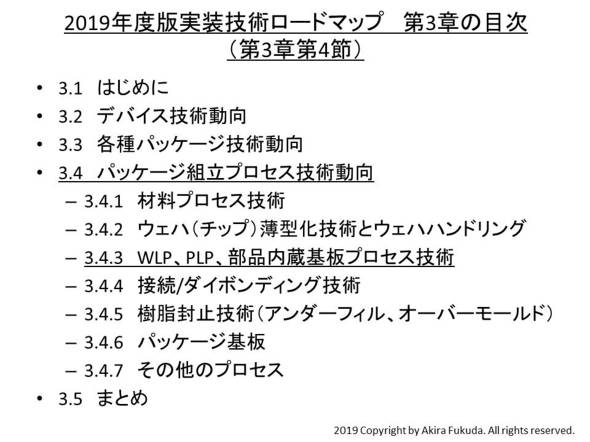

本シリーズの第23回から、第3章「電子デバイスパッケージ」の概要を紹介している。「電子デバイスパッケージ」は第1節から第5節までの5つの節によって構成される。「3.1 はじめに」「3.2 デバイス技術動向」「3.3 各種パッケージ技術動向」「3.4 パッケージ組立プロセス技術動向」「3.5 まとめ」である。本シリーズの第27回からは、第3章第4節「3.4 パッケージ組立プロセス技術動向」の概要をご紹介してきた。

2019年6月4日に東京で開催された「2019年度版 実装技術ロードマップ」完成報告会のプログラム。本シリーズの第23回から第3章「電子デバイスパッケージ」(プログラムの7番)の概要を解説している。出典:JEITA(クリックで拡大)

前回は、微細配線を形成可能な「FO-WLP(Fan Out-Wafer Level Package)」の組み立て工程を説明した。今回は、部品内蔵基板の組み立て工程をご紹介する。

部品内蔵基板とはその名称の通り、半導体チップや受動部品などを内蔵させたプリント配線基板である。部品を内蔵するので実装面積の削減になる。また部品と基板の接続部における寄生素子が減るので、回路動作の高速化を見込める。

Copyright © ITmedia, Inc. All Rights Reserved.