電子回路を雑音から保護する積層チップバリスタ:福田昭のデバイス通信(233) 2019年度版実装技術ロードマップ(43)(1/2 ページ)

今回から、EMC対策部品のうち、電子回路を雷サージや静電気放電(ESD)などの雑音から保護する部品を説明する。まずは「積層チップバリスタ」について解説する。

雷サージやESDなどを吸収する電子部品

電子情報技術産業協会(JEITA)が発行した「2019年度版 実装技術ロードマップ」に関する完成報告会(2019年6月4日に東京で開催)と同ロードマップの概要をシリーズでご報告している。今回はその第43回である。

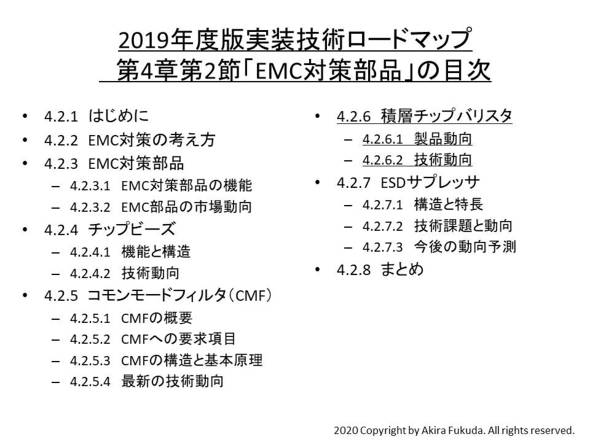

本シリーズの第31回から、第4章「電子部品」の概要を説明してきた。第4章「電子部品」は、「4.1 LCR部品」「4.2 EMC対策部品」「4.3 センサ」「4.4 コネクタ」「4.5 入出力デバイス」の5つの節に分かれる。第39回からは、「4.2 EMC対策部品」の概要を紹介している。第40回は雑音対策部品の代表である「チップビーズ(チップフェライトビーズ、チップ型フェライトビーズインダクタ)」の概要を、第41回と第42回は同じく雑音対策部品の代表である「コモンモードフィルタ(コモンモードチョークコイル)」の概要をご紹介した。

2019年6月4日に東京で開催された「2019年度版 実装技術ロードマップ」完成報告会のプログラム。本シリーズの第31回から、第4章「電子部品」(プログラムの8番)の概要を紹介している。出典:JEITA(クリックで拡大)

今回からは、EMC対策部品の中でも、電子回路を雷サージや静電気放電(ESD)などの雑音から保護する部品を説明していく。初回である今回は「積層チップバリスタ」の概要を述べる。積層チップバリスタは「バリスタ」の一種である。そこで始めは「バリスタ」について解説する。

「バリスタ」は2端子部品であり、通常は非常に高い抵抗値を有する絶縁素子である。材料には酸化亜鉛(ZnO)やチタン酸ストロンチウム(SrTiO3)などのセラミックスが使われる。

バリスタは電源線(あるいは信号線)と接地線(グランド)の間に挿入して使う。電源ライン(あるいは信号ライン)が正常に働いているときは、絶縁素子であるバリスタはコンデンサに見える。ここで雷サージや静電気放電(ESD)などの高電圧電流パルスが電源ライン(あるいは信号ライン)に侵入してバリスタに加わると、バリスタの抵抗値が急激に減少する。バリスタの中を電流が通過し、電源ライン(あるいは信号ライン)の電圧が低下する。このようにして電子回路を高電圧の電流パルスから保護する。

クランプ電圧、バリスタ電圧、サージ耐量、最大許容回路電圧

バリスタの基本特性を表す仕様には、「クランプ電圧(制限電圧)」「バリスタ電圧」「サージ電流耐量」「最大許容回路電圧」などがある。「クランプ電圧(制限電圧)」は、高電圧の電流パルス(電流波形の立ち上がり時間(厳密には波頭長)8マイクロ秒、半値幅(厳密には波尾長)20マイクロ秒)をバリスタに印加したときに、バリスタの端子間に発生する電圧である。バリスタが電流パルスを吸収したあとに、保護対象である電子回路に加えられる電圧を意味する。

「バリスタ電圧」は、バリスタの端子間に1mAの電流が流れるときの端子間電圧である。バリスタ電圧よりも低い電圧ではバリスタは動作しておらず(コンデンサ状態)、バリスタ電圧よりも高い電圧では、バリスタは動作している(低抵抗素子状態)とみなせる。

「サージ電流耐量」は、バリスタが耐えられる電流パルスの大きさである。高電圧の電流パルス(電流波形の立ち上がり時間(厳密には波頭長)8マイクロ秒、半値幅(厳密には波尾長)20マイクロ秒)をバリスタに5分間隔で2回印加したときに、バリスタ電圧の変化が10%以下となる電流パルスの最大値で表す。

「最大許容回路電圧」は、バリスタに連続して印加できる電圧の最大値である。直流と交流で最大許容回路電圧は異なる。最大許容電圧を超える電圧をバリスタに加え続けると、バリスタは劣化し、さらには破壊に至る。

Copyright © ITmedia, Inc. All Rights Reserved.