3D NANDの最新動向、覇権争いの鍵となる技術は? バーチャル開催の「IMW2020」から:湯之上隆のナノフォーカス(26)(4/5 ページ)

半導体メモリの国際学会「インターナショナル・メモリ・ワークショップ(IMW)2020」が5月17日〜20日の4日間、バーチャル方式で開催された。本稿では、チュートリアルの資料を基に、NAND型フラッシュメモリメーカー各社の現状とロードマップを紹介する。

3次元NANDの各社の現状

チュートリアル「PART I - 3D NAND」の3人目は、Applied Materials(AMAT)のTomohiko Kitajima氏の講演で、タイトルは、“Materials and process technology driven 3D NAND Scaling beyond 200 pairs”だった。この講演では、NANDメーカー各社の現状を分かりやすく比較し、さらに今後のロードマップが説明された。3次元NANDを理解する上で、大変有意義な講演であり、筆者は、学会期間中、繰り返して動画を視聴した。以下に、その一部を紹介する。

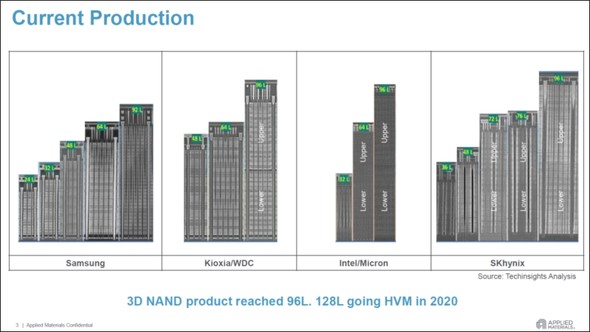

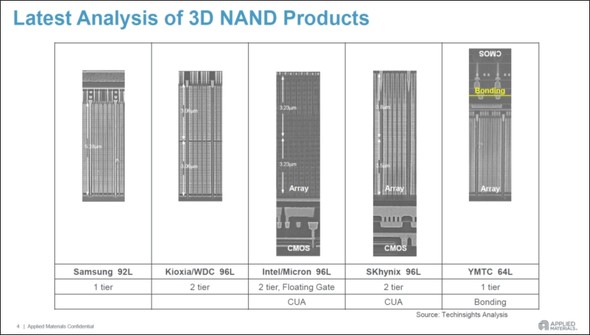

図11に、NANDメーカー各社が製造した3次元NAND全ての断面SEM写真を示す。また、図12に、各社の最新の3次元NANDのSEM写真と構造の特徴を示す。この2枚のスライドに、筆者は圧倒された。そして、この2枚のスライドのためだけに、ドイツのドレスデンに行ってもいいと思ったほど、価値があると感じた。

図11:メモリメーカー各社の3次元NANDの断面SEM写真 出典:Tomohiko Kitajima, Applied Materials, “Materials and process technology driven 3D NAND Scaling beyond 200 pairs ”, IMW2020, Tutorials PART 1.(クリックで拡大)

図12:メモリメーカー各社の最新の3次元NANDの比較 出典:Tomohiko Kitajima, Applied Materials, “Materials and process technology driven 3D NAND Scaling beyond 200 pairs ”, IMW2020, Tutorials PART 1.(クリックで拡大)

先行したSamsungが直面した課題

あらためて図11を見てみよう。この1枚だけからも、各社および各グループの技術、戦略、悩みなどが見て取れる。

Samsung Electronicsは、24層、32層、48層、64層、92層と3次元の多層化を進めている。中国の西安工場で大量生産して出荷を開始したのは48層からであるから、24層と32層はサンプル出荷品であろう。Samsungは、どこよりも早く48層を出荷し、64層も発売したので、この二つの世代で世界を制した。

その競争力の源泉は、アスペクト比(Aspect Ratio、AR)の大きなメモリホールのドライエッチング技術にあったと考えられる。SamsungはLam Researchとの共同開発により、ARの大きなHARC(High Aspect Ratio Contact)エッチング装置と技術を開発し、他社を大きくリードした。

ところが、64層の次の世代でSamsungは大きくつまずいてしまった。他社が96層を製造しているのに、Samsungだけが92層という中途半端な積層数になっている。しかも、断面図の高さから、他社より4層少ないことを割り引いたとしても、Samsungの92層は、他社の96層より随分縦方向の寸法が小さいことが分かる。

これは、キオクシア&WDをはじめとする他社が、96層を48層の2段積みで形成しているのに対して、Samsungだけが一括加工でメモリホールのHARCエッチを行っていることに起因する。

というのは、ARが大きくなればなるほど、HARCエッチが難しくなるからである。具体的に言うと、エッチ速度が指数関数的に遅くなるし、さまざまなモードの形状異常が多発する上、ホール径のばらつきの制御が困難になるのである。

そのため、Samsungは、他社より4層少ない92層とし、さらにメモリセルを縦に方向にシュリンクして、少しでもHARCのARを小さくしようとしていると考えられる。しかし、それでもなお、Samsungの92層の歩留りは相当悪いと推測していた。

という状況にもかかわらず、Samsungは2019年11月19日、次世代の128層についても、一括加工で製造することを発表した(PC Watch「Samsung、128層シングルスタックの第6世代「V-NAND」を2020年市場投入」)。筆者は、一括加工にこだわるほど、自分で自分の首を絞めかねないと思っており、Samsungの先行きが懸念される。

96層を制したのはキオクシア&WD

HARCエッチ技術に自信があるが故につまずいてしまったSamsungに替わって、96層で世界を制したのはキオクシア&WDである。筆者がサプライヤーなどから得ていた情報では、2019年第4四半期時点で、四日市工場における96層の稼働キャパシティーは、Samsungの3〜4倍もあった。

なぜ、キオクシア&WDは、96層で成功を収めることができたのか?

キオクシア&WDは、64層まではHARCエッチの技術開発でSamsungに大きく後れを取っていた。そのため、96層については、早々に、48層の2段積みを選択したと思われる。

図11を見ると、Samsung以外の各社の96層は、LowerとUpperに分かれている。この2段積み方式で96層を形成する場合、12インチウエハー全体で約2兆個に及ぶメモリホールの位置合わせが難しい。四日市工場でも、この問題により、歩留りが上がらない時期があったと推測された。

ところが、2019年の夏頃から、風向きが変わってきた。筆者のキオクシアの知人らが、「500層でも積めと言われれば積みますけどね」と言い始めたのである。メモリホールの位置合わせ技術について、何らかのブレークスルーがあったのではないかと思われた。そして、NAND各社の稼働キャパシティーを調べたところ、前述の通り、四日市工場の96層が圧倒的な規模であることが分かったわけだ。

再度、図11を見てみよう。Intel&Micronは64層以降、2段積みを採用している。また、SK hynixは、(64層ではなく中途半端な)72層以降、2段積みを採用している。

そして、これら各社の2段積みと比較すると、キオクシア&WDでは、LowerとUpperのつなぎ目が非常にくっきりしていることが分かる。恐らく、キオクシア&WDは、LowerとUpperの間に、メモリホールの合わせずれを解決できる何らかの構造を取り入れていると考えられる。それが、2段積みの歩留りを飛躍的に向上させ、Samsungをはるかに超える稼働キャパシティーで96層を製造するに至ったのではないかと考えている。

SamsungはHARCエッチに自信があったが故につなずいたが、キオクシア&WDは一括加工を早々に諦めたために96層の2段積みで成功した。このことは、2020年1月23日に亡くなったハーバード・ビジネススクールのクリステンセン教授が提唱した“イノベーションのジレンマ”を彷彿(ほうふつ)とさせる。

各社の最新の3次元NAND

今度は、各社の最新の3次元NANDを比較した図12を見てみよう。ここで最も注目したのは、中国の紫光集団傘下の長江ストレージ(YMTC、旧XMC)の3次元NANDである。

(再掲)図12:メモリメーカー各社の最新の3次元NANDの比較 出典:Tomohiko Kitajima, Applied Materials, “Materials and process technology driven 3D NAND Scaling beyond 200 pairs ”, IMW2020, Tutorials PART 1.(クリックで拡大)

YMTCは、2016年3月に突然、3次元NANDへの参入を発表した。YMTCは、日韓台などの半導体メーカーの技術者を高待遇で募集し、まず32層の開発に取り組んだ。1年ほどで32層の動作に成功すると、次は48層をスキップして64層の開発に着手した。そして、YMTCは2019年9月17日に、64層を量産することを発表した(参考)。

そのYMTCの64層は、データの読み出しや書き込みを制御するCMOS回路を、メモリセルとは別のウエハーで製造し、それぞれをボンディングにより張り合わせる構造となっている。

チップ当たりのメモリ密度を増大させるために、CMOS回路をメモリセルの下部に作り込むCUA(CMOS Under Array)が一般的であり、実際にIntel&MicronやSK hynixが採用している。しかし、YMTCが独自技術を開発したことが、半導体業界にちょっとした衝撃を与えた。

YMTCの64層の稼働キャパシティーは、2019年第4四半期時点で2万枚弱しかなかった。しかし、YMTCは、2020年4月12日に、128層で、1.33テラビット、QLCの3次元NANDの開発に成功したと発表している(参考)。今後、YMTCが台風の目になる可能性がある。

Copyright © ITmedia, Inc. All Rights Reserved.