3D NANDの最新動向、覇権争いの鍵となる技術は? バーチャル開催の「IMW2020」から:湯之上隆のナノフォーカス(26)(5/5 ページ)

半導体メモリの国際学会「インターナショナル・メモリ・ワークショップ(IMW)2020」が5月17日〜20日の4日間、バーチャル方式で開催された。本稿では、チュートリアルの資料を基に、NAND型フラッシュメモリメーカー各社の現状とロードマップを紹介する。

3次元NANDのロードマップ

誰もが想像もできなかったコロナ禍によって、テレワーク、オンライン授業、オンライン診療などが普及した。IMW2020もバーチャルでの開催となった。その結果、データセンターの需要が急拡大しており、サーバ用NAND市場も急成長している。

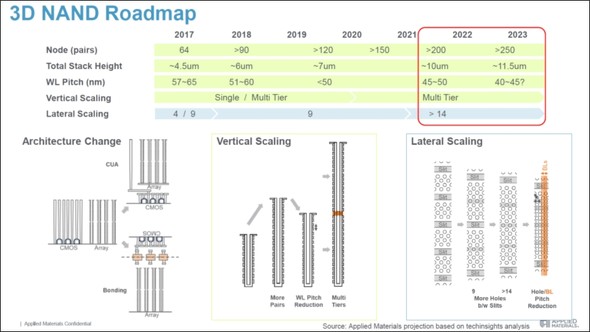

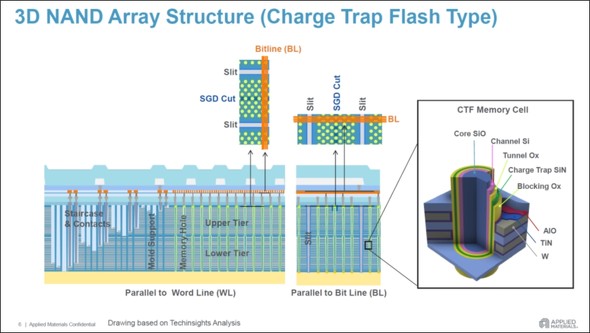

それに伴って、3次元NANDは、さらなる高密度化が期待されている。そのR&Dのロードマップを図13に示す。現在、各社は128層(キオクシア&WDは112層)の量産を立ち上げようとしている。その後、さらに積層数を増やしていき、2021〜2022年に200層以上、2022〜2023年に250層以上を開発するというロードマップになっている。尚、このロードマップでは、代表的な3次元NANDの構造とし、てチャージ・トラップ方式の図14を想定している。

図13:3次元NANDのR&Dのロードマップ 出典:Tomohiko Kitajima, Applied Materials, “Materials and process technology driven 3D NAND Scaling beyond 200 pairs ”, IMW2020, Tutorials PART 1.(クリックで拡大)

図14:チャージ・トラップ方式の代表的な3次元NAND構造 出典:Tomohiko Kitajima, Applied Materials, “Materials and process technology driven 3D NAND Scaling beyond 200 pairs ”, IMW2020, Tutorials PART 1.(クリックで拡大)

このような多層化を実現するためには、図13の下段に示したような開発が必要不可欠となる。まず、左端の“Architecture Change”は、CMOS回路をメモリセルの下に配置したり(CUA)、YMTCのように上にボンディングすることにより、チップ面積当たりのメモリ密度を増大する技術である。既に、多くのNANDメーカーが取り入れている。

次に、“Vertical Scaling”では、縦方向にどれだけ多数のメモリセルを積層するかという技術である。この図には、そのトレンドが分かりやすく書かれている。まず、単純にセル数を増大させる“More Pairs”がある。次に、既にSamsungが取り入れた”WL(Ward Line)Pitch Reduction“がある。これは、メモリセルの縦方向のサイズをシュリンクする方法である。この手法を適用すると、同じPair数ならば、Stack Hightを低くすることができるため、メモリホールのHARC加工がやりやすくなる。

そして、“WL Pitch Reduction”を続けながら、“More Pairs”を継続して行くと、いずれは“Multi Tiers”(多段積み)を行うことになる。Samsung以外は既に量産適用している。そして、Samsungもいずれは、“Multi Tiers”に移行せざるを得なくなるだろう。そして、全てのNANDメーカーが2段、3段、4段と多段化を進めていくことになると考えられる。

さらに、メモリ密度を増大させる手法として、“Lateral Scaling”がある。これは、横方向にシュリンクすることにより、チップ当たりのメモリ密度を増大する手法である。この“Lateral Scaling”には、二つの手段があり、一つは、SlitとSlitの間のメモリホールの数を、現在の9個から14個へ同大させる“More Holes b/w Slits”である。もう一つは、メモリホールの直径をシュリンクし、より高密度にメモリホールをつくりこむ“Hole BL(Bit Line) Pitch Reduction”である。

しかし、これらの二つの開発は、HARCエッチを行い、または“More Pairs”を形成しながら行うため、課題が山積している。NANDメーカー各社は、デバイス構造、材料、プロセスフローなどに知恵を絞り、製造装置メーカーや材料メーカーと共同開発を行いながら、メモリの高密度化にまい進するのだろう。

そして、48層と64層を制したSamsungに取って代わって、96層はキオクシア&WDがリードしたように、高密度化の技術でブレークスルーしたNANDメーカーが次世代の覇権を握ると思われる。それは一体どこになるのだろうか? その兆候は、次回ドイツのドレスデンで開催されるIMW2021でつかむことができるかもしれない。来年(2021年)はぜひ、リアルなIMW2021を取材したいと思う(バーチャルも併用して頂けるとなおうれしい)。

オンラインセミナー開催のお知らせ

2020年7月7日(火)13:00〜、サイエンス&テクノロジー主催で、『コロナ禍の半導体産業を生き抜くための羅針盤』と題するオンラインセミナーを開催します。詳細は、こちらのサイトをご参照ください。

筆者プロフィール

湯之上隆(ゆのがみ たかし)微細加工研究所 所長

1961年生まれ。静岡県出身。京都大学大学院(原子核工学専攻)を修了後、日立製作所入社。以降16年に渡り、中央研究所、半導体事業部、エルピーダメモリ(出向)、半導体先端テクノロジーズ(出向)にて半導体の微細加工技術開発に従事。2000年に京都大学より工学博士取得。現在、微細加工研究所の所長として、半導体・電機産業関係企業のコンサルタントおよびジャーナリストの仕事に従事。著書に『日本「半導体」敗戦』(光文社)、『「電機・半導体」大崩壊の教訓』(日本文芸社)、『日本型モノづくりの敗北 零戦・半導体・テレビ』(文春新書)。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

プロセッサ市場の下剋上なるか? Intelを追うAMDを躍進させた2人の立役者

プロセッサ市場の下剋上なるか? Intelを追うAMDを躍進させた2人の立役者

プロセッサ市場では、ある異変が起きている。Intelが長年トップに君臨しているこの市場で、AMDがシェアを急速に拡大しているのだ。今回は、AMDの躍進の背景にいる2人の立役者に焦点を当てよう。 “アフター・コロナ”の半導体産業を占う 〜ムーアの法則は止まるのか

“アフター・コロナ”の半導体産業を占う 〜ムーアの法則は止まるのか

新型コロナウイルス(COVID-19)の影響は各方面に及んでいる。もちろん半導体業界も例外ではない。最先端の微細化など次世代の技術開発ができない、製造装置が入手できない――。半導体産業では、これが現在の最大の問題である。本稿では、なぜそうなのか、今後どうなるのかを考察する。 半導体メーカーの働き方改革 〜半導体技術者の在宅勤務は可能か?

半導体メーカーの働き方改革 〜半導体技術者の在宅勤務は可能か?

今回は、いつもとは毛色を変えて、“半導体メーカーの働き方改革”に目を向けてみたい。筆者がメーカー勤務だった時代と現在とでは、働き方にどのような違いがあるのだろうか。 「VLSIシンポジウム2020」は初のオンライン開催に

「VLSIシンポジウム2020」は初のオンライン開催に

2020年6月15〜18日(以下、特に記載がない限り全てハワイ時間)に開催される半導体デバイス/回路技術に関する国際会議「VLSIシンポジウム 2020」。本来は米国・ハワイで開催される予定だったが、新型コロナウイルス感染症(COVID-19)の影響で、初のオンライン開催となる。VLSIシンポジウム委員会は2020年5月20日、記者説明会をオンラインで開催し、概要を説明した。 HDD大手Seagateは4四半期連続で前期比の売り上げが増加

HDD大手Seagateは4四半期連続で前期比の売り上げが増加

今回は、米Seagate Technologyの2020会計年度第3四半期(2020年1〜3月期)の業績を紹介する。