多層配線の性能を向上させるエアギャップと2次元材料:福田昭のデバイス通信(290) Intelが語るオンチップの多層配線技術(11)(1/2 ページ)

今回は、多層配線の容量を下げる要素技術「エアギャップ」と、多層配線の抵抗を下げる要素技術「2次元(2D)材料」について解説する。

配線の容量と抵抗を低減する要素技術

半導体のデバイス技術と回路技術に関する国際学会「VLSIシンポジウム」では、「ショートコース(Short Course)」と呼ぶ技術講座を開催してきた。2020年6月に開催されたVLSIシンポジウムのショートコースは、3つの共通テーマによる1日がかりの技術講座が設けられていた。その中で「SC1:Future of Scaling for Logic and Memory(ロジックとメモリのスケーリングの将来)」を共通テーマとする講演、「On-Die Interconnect Challenges and Opportunities for Future Technology Nodes(将来の技術ノードに向けたオンダイ相互接続の課題と機会)」が非常に興味深かった。そこで講演の概要を本コラムの第280回からシリーズでお届けしている。講演者はIntelのMauro J. Kobrinsky氏である。

なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

本シリーズの第5回からは、多層配線の微細化と性能向上を両立させる要素技術を紹介している。前回は、配線のアスペクト比(AR:Aspect Ratio)を高める2つの要素技術を概説した。今回は、多層配線の容量を下げる要素技術「エアギャップ」と、多層配線の抵抗を下げる要素技術「2次元(2D)材料」をそれぞれ紹介する。

究極の低誘電率材料「空気(エア)」を絶縁膜に

多層配線の配線間容量を下げる基本的な方法は、層間絶縁膜に誘電率の低い絶縁材料を使うことである。標準的な絶縁膜である二酸化シリコン(SiO2)膜の比誘電率は3.9〜4.3とかなり高い。130nm世代のロジックではフッ素(F)でSiO2の酸素(O)を置換したSiOFを採用した。SiOFの比誘電率は3.4〜3.7と低い。90nm世代のロジックでは、炭素(C)で酸素を置換したSiOCを導入した。SiOCの比誘電率は2.7〜2.9とさらに低い。65nm世代のロジックでは、ポリアリーレン(PAr:Poly-Arylene)膜を層間絶縁膜に組み込んでSiOCとの積層構造とした。ポリアリーレン膜の比誘電率は2.65とかなり低い。

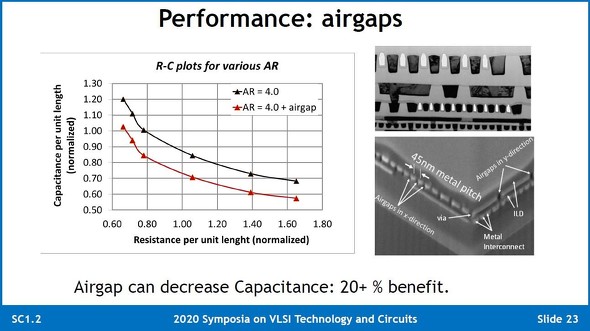

究極の低誘電材料は空気(エア)、あるいは真空だ。比誘電率は1.0とあらゆる材料の中で最も低い。この空隙を隣接配線間に意図的に導入するのが「エアギャップ(Airgap)技術」である。講演では例えばアスペクト比(AR)が4の配線構造の場合、エアギャップ技術の採用によって容量が約20%減少したとする。なお、エアギャップ技術は高性能プロセッサの多層配線に採用済みだ。

Copyright © ITmedia, Inc. All Rights Reserved.