多層配線のアスペクト比(AR)を高める2つの要素技術:福田昭のデバイス通信(289) Intelが語るオンチップの多層配線技術(10)

配線のアスペクト比(AR)を高める、2つの要素技術について解説する。

ボトムアップで銅をビアと溝に埋め込む

半導体のデバイス技術と回路技術に関する国際学会「VLSIシンポジウム」では、「ショートコース(Short Course)」と呼ぶ技術講座を開催してきた。2020年6月に開催されたVLSIシンポジウムのショートコースは、3つの共通テーマによる1日がかりの技術講座が設けられていた。その中で「SC1:Future of Scaling for Logic and Memory(ロジックとメモリのスケーリングの将来)」を共通テーマとする講演、「On-Die Interconnect Challenges and Opportunities for Future Technology Nodes(将来の技術ノードに向けたオンダイ相互接続の課題と機会)」が非常に興味深かった。そこで講演の概要を本コラムの第280回からシリーズでお届けしている。講演者はIntelのMauro J. Kobrinsky氏である。

なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

本シリーズの第5回からは、多層配線の微細化と性能向上を両立させる要素技術を紹介している。前回は、配線のアスペクト比(AR)と配線抵抗および配線容量の関係を概説した。ARを高くすると配線の抵抗と容量がともに減少すること、標準的なプロセスではARの高さはおよそ3前後になることを述べた。今回はARをさらに高める、2つの要素技術をご報告する。

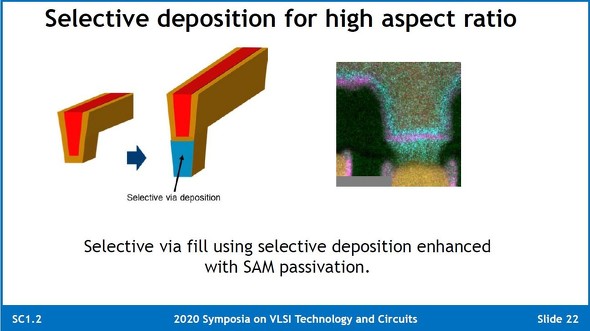

アスペクト比(AR)の高い配線を実現する埋め込み技術。左端の写真は標準的なプロセスによる配線(ビアを含む)の断面観察像。配線内に空隙(ボイド(Void))が発生してしまう。その右隣は新しく開発したプロセスによる配線(ビアを含む)の断面観察像。銅(Cu)がきれいに埋め込まれている。右端は新しく開発したプロセスの概念図。銅がボトムアップで堆積する。出典:Intel(クリックで拡大)

標準的なプロセスでは、ビアと溝(配線層部分)の内壁に極めて薄い銅(Cu)の層(シード層)をスパッタリングで形成後、電解メッキによってCu薄膜を堆積させる。このときARがあまり高くなると、溝の開口部近くで堆積したCu薄膜同士が接触しやすくなる(オーバーハング)。接触するとビア側のCu薄膜の堆積が止まり、配線断面に空隙(ボイド(Void))を形成してしまう。ボイドの存在は、配線抵抗の上昇やエレクトロマイグレーション耐性の低下などにつながる。

新しく開発したプロセスでは、Cu薄膜の堆積速度が溝の底面と側面で異なる。溝の底面からの堆積速度が高い。すなわちボトムアップで堆積する。溝の開口部は最後にCuが堆積するので、ボイドが発生しない。

講演スライドでは、開発したプロセスの詳細には言及していない。筆者の調べによると、少なくとも3種類の候補技術をIntelは過去に発表済みだ。1つは、電解メッキのメッキ液に添加する抑制剤の濃度を最適化する手法である。もう1つは、ルテニウム(Ru)の極めて薄い層を拡散バリア層の上に形成し、ライナー層とすること。ライナー層の上にCu層が電解メッキによって堆積すると、オーバーハングが起こりにくくなる。3番目は電解メッキではなく、無電解メッキによってCu層を堆積することである。

選択堆積でビア部分だけに金属を埋め込む

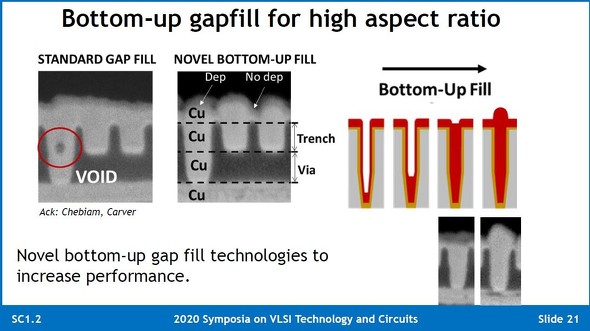

もう1つの要素技術は、Cu層の形成を2段階に分けることである。始めに選択堆積(Selective Deposition)技術によってビア部分だけに金属を埋め込む。次に電解メッキによって銅を溝(配線層部分)に堆積する。こうすると電解メッキで堆積させる部分のARが低下し、ボイドのない埋め込みが容易になる。

選択堆積技術は、自己組織化単分子(SAM:Self-Assembled Monolayer)膜をフィルターに使うことで選択性が高まる。SAM膜を表面に付着させた部分は、金属が堆積しない。SAM膜を使った選択堆積技術については後ほど、もう少し詳しく説明する。

(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

多層配線のアスペクト比(AR)と抵抗および容量の関係

多層配線のアスペクト比(AR)と抵抗および容量の関係

今回は、配線のアスペクト比(AR)と配線抵抗および配線容量の関係を概説する。 銅(Cu)配線の微細化と抵抗値の増大

銅(Cu)配線の微細化と抵抗値の増大

引き続き、オンチップの多層配線技術に関するIntelの講演内容を紹介する。今回は、銅配線の寸法と電気抵抗の関係を説明する。 ムーア則の維持に貢献する配線技術

ムーア則の維持に貢献する配線技術

「VLSIシンポジウム」から、オンチップの多層配線技術に関するIntelの講演内容を紹介するシリーズ。将来の配線技術には、サブトラクティブ法や低誘電率絶縁材料などに期待がかかっている。 オンチップの相互接続技術を過去から将来まで概観

オンチップの相互接続技術を過去から将来まで概観

2020年6月にオンラインで開催された「VLSIシンポジウム」から、オンチップの多層配線技術に関するIntelの講演内容を紹介する。 HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

今回は、米Western Digitalの2021会計年度第1四半期の業績を紹介する。 HDD大手Seagateの四半期売上高は前年同期比で2桁の減少

HDD大手Seagateの四半期売上高は前年同期比で2桁の減少

今回は、米Seagate Technologyの2021会計年度第1四半期の業績を紹介する。