連載

作り手の“腕の見せ所”、「Apple Silicon M1」の層数を解析する:この10年で起こったこと、次の10年で起こること(50)(2/4 ページ)

今回は、「Apple Silicon M1」の断面を解析し、層数や配線について解説する。配線に満ちている電子機器では、配線や配置は「腕の見せ所」ともいえる重要な技術だ。

「Apple Silicon M1」の断面図

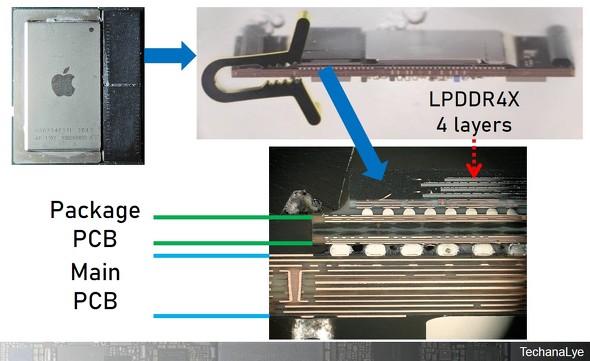

図2は、Apple Silicon M1を基板ごと樹脂で固めて切断し、表面を研磨して配線構造を可視化した様子(右上)と、M1パッケージに搭載されるLPDDR4X DRAM部の拡大写真である。

上からDRAMのシリコンが4枚、DRAMのパッケージ基板、DRAM基板とパッケージ接続用のボール、M1パッケージ、M1パッケ―ジとメインの基板の接続ボール、メイン基板、基板裏面側のコンデンサーやインダクターの断面である。おのおのの配線層数や接続関係が分かるものとなっている。平面の解析と合わせて複数箇所の断面を観察すれば、配線経路なども分かる(本稿では記載しない)。

メモリは4枚重ね、M1パッケージは8層構造、メイン基板は12層構造であることが明確になった。

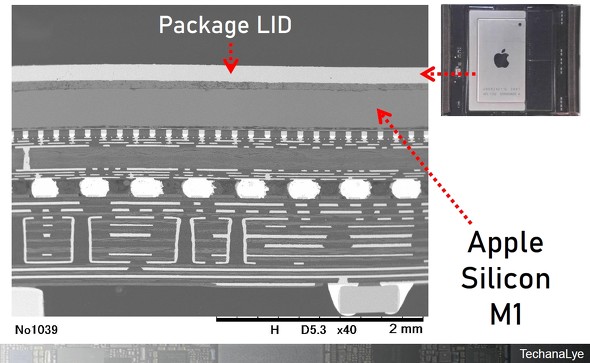

図3はApple Silicon M1のSoC(System On Chip)部の断面の様子である。上からチップを覆う金属製のLID、LIDとシリコンの間の接着剤(放熱効果もある)、シリコン、シリコン直下のInFO配線、M1パッケージ、パッケージとメイン基板を接続するボール、メイン基板、直下のセラミックコンデンサーとなっている。

さらに拡大するとシリコンの配線層数までも明確になっている。

Copyright © ITmedia, Inc. All Rights Reserved.