3D NANDƒtƒ‰ƒbƒVƒ…‚جچ‚‘w‰»‚ئ‹L‰¯–§“x‚جگ„ˆعپF•ں“cڈ؛‚جƒXƒgƒŒپ[ƒW’تگMپi186پj ƒAƒiƒٹƒXƒg‚ھŒê‚é•sٹِ”گ«ƒپƒ‚ƒٹ‚جچإگV“®Œüپi13پjپi2/2 ƒyپ[ƒWپj

چ،‰ٌ‚حپA3D NANDƒtƒ‰ƒbƒVƒ…‹Zڈp‚جچ‚–§“x‰»‚ً‚¯‚ٌˆّ‚µ‚ؤ‚«‚½چ‚‘w‰»‚ئ‘½’l‰»‚جگ„ˆع‚ة‚آ‚¢‚ؤ‰ًگà‚·‚éپB

’´چ‚‘wƒrƒ‹ƒfƒBƒ“ƒO‚ئ‰»‚·3D NAND‚جƒپƒ‚ƒٹƒZƒ‹ƒAƒŒƒC

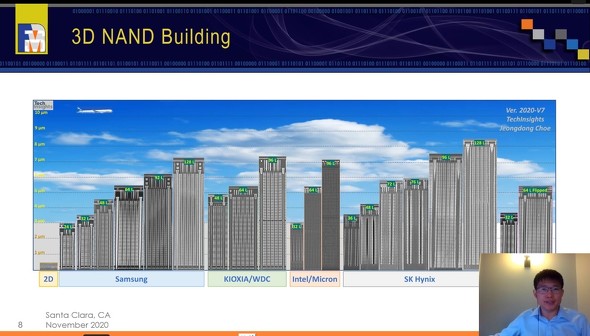

پ@3D NANDƒtƒ‰ƒbƒVƒ…‚جچ‚‘w‰»‚ح‚µ‚خ‚µ‚خپAچ‚‘wƒrƒ‹ƒfƒBƒ“ƒO‚ة—ل‚¦‚ç‚ê‚éپB‘خ‚·‚éƒvƒŒپ[ƒiپ[پi2DپjNANDƒtƒ‰ƒbƒVƒ…‚ح‚³‚µ‚¸‚كپA•½‰®‚ ‚é‚¢‚ح’ل‘w‚جƒAƒpپ[ƒgƒپƒ“ƒg‚¾‚낤‚©پB

پ@2D NANDƒtƒ‰ƒbƒVƒ…‚جچ‚‚³‚حپA1ƒتm‚ة–‚½‚ب‚¢پB‚±‚ê‚ة‘خ‚µ‚ؤ3D NANDƒtƒ‰ƒbƒVƒ…‚ح24‘wپ`32‘w‚إٹù‚ة3ƒتm‘OŒم‚ئپA‘ه‹K–ح”¼“±‘جڈWگد‰ٌکHپiLSIپj‚ئ‚µ‚ؤ‚حˆظڈي‚بچ‚‚³‚ة’B‚µ‚ؤ‚¢‚½پB64‘w‚ح5ƒتm‘OŒمپA72‘w‚ح6ƒتm‘OŒم‚ئ‚³‚ç‚ةچ‚‘w‰»‚·‚éپB96‘w‚ح7ƒتm‘OŒم‚ة’B‚·‚éپB

پ@چ‚‘w‰»‚حپAƒپƒ‚ƒٹƒZƒ‹‚ًڈc•ûŒü‚ةگع‘±‚·‚éچEپiپuƒپƒ‚ƒٹƒXƒ‹پ[ƒzپ[ƒ‹پv‚ئŒؤ‚شپj‚جŒ`گ¬‚ً’ک‚µ‚“‚‚·‚éپB‚±‚ج‚½‚كپAƒپƒ‚ƒٹƒXƒ‹پ[ƒzپ[ƒ‹‚جŒ`گ¬‚ً2’iٹK‚إژہژ{‚·‚éƒvƒچƒZƒX‚ھچج—p‚³‚ê‚ؤ‚¢‚éپB—ل‚¦‚خ64‘w‚إ‚ ‚ê‚خپA32‘w‚جƒXƒ‹پ[ƒzپ[ƒ‹‚ً2‰ٌŒ`گ¬‚·‚éچH’ِ‚ة•ھ‚¯‚éپB

3D NANDƒtƒ‰ƒbƒVƒ…‚جچ‚‘wƒrƒ‹ƒfƒBƒ“ƒOپB”z•zژ‘—؟‚إ‚ح”–‚¢ƒAƒ~‚ً‚©‚¯‚ؤ‚¢‚½پBڈo“TپFFMS 2020‚جچu‰‰پuTechnology TrendپFNAND پ• Emerging Memoryپv‚ج”z•zژ‘—؟پiƒNƒٹƒbƒN‚إٹg‘هپj

3D NANDƒtƒ‰ƒbƒVƒ…‚جچ‚‘wƒrƒ‹ƒfƒBƒ“ƒOپBچu‰‰ƒXƒ‰ƒCƒh‚إ‚حƒپƒ‚ƒٹƒZƒ‹ƒAƒŒƒC‚ج’f–ت‚ً“dژqŒ°”÷‹¾‚إٹدژ@‚µ‚½‰و‘œ‚ًژ¦‚µ‚ؤ‚¢‚½پBڈo“TپFFMS 2020‚جچu‰‰پuTechnology TrendپFNAND پ• Emerging Memoryپv‚جƒXƒ‰ƒCƒhپiƒNƒٹƒbƒN‚إٹg‘هپj

پ@‚ب‚¨Samsung‚¾‚¯‚حپAƒپƒ‚ƒٹƒXƒ‹پ[ƒzپ[ƒ‹‚جŒ`گ¬‚ً1‰ٌ‚إچد‚ـ‚¹‚ؤ‚¢‚éپB“¯‚¶گد‘wگ”‚إ‚àپASamsung‚ج3D NAND‚ح‚ ‚ـ‚èچ‚‚‚ب‚¢پB“ء‚ة92‘w‚ئ128‘w‚إ‚حپA‘¼ژذ‚ة”ن‚ׂؤ’ل‚¢پBƒپƒ‚ƒٹƒXƒ‹پ[ƒzپ[ƒ‹چىگ¬‚ج“‚³‚ًٹةکa‚µ‚ؤ‚¢‚邱‚ئ‚ھ‚¤‚©‚ھ‚¦‚éپB

پiژں‰ٌ‚ة‘±‚پj

پثپu•ں“cڈ؛‚جƒXƒgƒŒپ[ƒW’تگMپvکAچعƒoƒbƒNƒiƒ“ƒoپ[ˆê——

Copyright © ITmedia, Inc. All Rights Reserved.

ٹضکA‹Lژ–

’†چ‘‚ج3D NANDƒtƒ‰ƒbƒVƒ…ƒپپ[ƒJپ[پuYMTCپv‚جŒ»ڈَ

’†چ‘‚ج3D NANDƒtƒ‰ƒbƒVƒ…ƒپپ[ƒJپ[پuYMTCپv‚جŒ»ڈَ

چ،‰ٌ‚حپA’†چ‘‚ج3D NANDƒtƒ‰ƒbƒVƒ…ƒxƒ“ƒ`ƒƒپ[‚إ‚ ‚éYMTCپiYangtze Memory Technologies Co., Ltd.پj‚جŒ»ڈَ‚ةٹض‚·‚éچu‰‰•”•ھ‚ًڈذ‰î‚·‚éپB چ‚‘w‰»‚جŒp‘±‚إپAگ»‘¢ƒRƒXƒg‚ً”ڑ‰؛‚°‚·‚é3D NANDƒtƒ‰ƒbƒVƒ…

چ‚‘w‰»‚جŒp‘±‚إپAگ»‘¢ƒRƒXƒg‚ً”ڑ‰؛‚°‚·‚é3D NANDƒtƒ‰ƒbƒVƒ…

چ،‰ٌ‚©‚ç‚حپA”¼“±‘جƒپƒ‚ƒٹ‚جƒAƒiƒٹƒXƒg‚إ‚ ‚éMark Webbژپ‚جپuFlash Memory Technologies and Costs Through 2025پiƒtƒ‰ƒbƒVƒ…ƒپƒ‚ƒٹ‚ج‹Zڈp‚ئƒRƒXƒg‚ً2025”N‚ـ‚إ“W–]‚·‚éپjپv‚ئ‘è‚·‚éچu‰‰‚جٹT—v‚ً‚²ڈذ‰î‚·‚éپB ƒ\ƒjپ[‚ھ20”N“x’تٹْ‹ئگر‚ًڈم•ûڈCگ³پACMOSƒZƒ“ƒTپ[‚à‘z’èڈم‰ٌ‚é

ƒ\ƒjپ[‚ھ20”N“x’تٹْ‹ئگر‚ًڈم•ûڈCگ³پACMOSƒZƒ“ƒTپ[‚à‘z’èڈم‰ٌ‚é

ƒ\ƒjپ[‚ح2021”N2Œژ3“ْپA2021”N3Œژٹْپi2020”N“xپj‘و3ژl”¼ٹْپi2020”N10پ`12ŒژٹْپjŒˆژZ‚ً”•\‚·‚é‚ئ‚ئ‚à‚ةپA2020”N“x’تٹْ‹ئگر—\‘z‚ًڈم•ûڈCگ³‚µ‚½پB ‘Oگi‚µ‘±‚¯‚éIntel

‘Oگi‚µ‘±‚¯‚éIntel

Intel‚ح2021”N1Œژ21“ْپi•ؤچ‘ژٹشپjپA‹ئگر”•\‚ًچs‚ء‚½پB‚»‚ê‚ًŒ©‚é‚ئپA“¯ژذ‚جپgڈI––ژŒvپh‚جƒJƒEƒ“ƒgƒ_ƒEƒ“‚ةپAڈ‚ب‚‚ئ‚àگ”•b‚ح’ا‰ء‚³‚ꂽ‚ئ‚¢‚¦‚邾‚낤پB‚½‚¾‚µپAٹ®‘S‚ةٹyٹدژ‹‚إ‚«‚é‚ي‚¯‚إ‚ح‚ب‚³‚»‚¤‚¾پBƒXƒsƒ“ƒhƒNƒ^پ[پiڈî•ٌ‘€چى‚ھ“¾ˆس‚بگlپj‚½‚؟‚حپAIntel‚ج2020”N‚ج‹ئگر‚جƒ}ƒCƒiƒX–ت‚¾‚¯‚ًٹب’P‚ة‹’²‚·‚邱‚ئ‚ھ‚إ‚«‚éپB‚ـ‚½پAƒvƒ‰ƒX–ت‚و‚è‚àŒ‡“_‚ج•û‚ة”½‰‚ًژ¦‚·“ٹژ‘‰ئ‚½‚؟‚à‚¢‚éپB HDD‘هژèWestern Digital‚ج‹ئگرپA‘O”N“¯ٹْ”ن‚ج‰c‹ئ—ک‰v‚ھ3ژl”¼ٹْکA‘±‚إ‘‰ء

HDD‘هژèWestern Digital‚ج‹ئگرپA‘O”N“¯ٹْ”ن‚ج‰c‹ئ—ک‰v‚ھ3ژl”¼ٹْکA‘±‚إ‘‰ء

چ،‰ٌ‚حپA•ؤWestern Digital‚ج2021‰ïŒv”N“x‘و1ژl”¼ٹْ‚ج‹ئگر‚ًڈذ‰î‚·‚éپB گVچق—؟‚إژںپXگ¢‘م‚ً‘_‚¤پu‹—U“d‘جƒپƒ‚ƒٹپiFeRAMپjپv

گVچق—؟‚إژںپXگ¢‘م‚ً‘_‚¤پu‹—U“d‘جƒپƒ‚ƒٹپiFeRAMپjپv

چ،‰ٌ‚حپu‹—U“d‘جƒپƒ‚ƒٹپiFeRAMپjپv‚ًژو‚èڈم‚°‚éپBFeRAM‚ج‹L‰¯Œ´—‚ئپA60”Nˆبڈم‚ة‹y‚شٹJ”‚ج—ًژj‚ًڈذ‰î‚µ‚و‚¤پB