埋め込みDRAMが大容量キャッシュの製造コスト低減に貢献:福田昭のストレージ通信(200) アナリストが語る不揮発性メモリの最新動向(25)

今回はDRAMをロジックLSIに埋め込む技術「eDRAM」の製品化事例を解説する。

ロジックLSIにDRAMを埋め込む

フラッシュメモリとその応用に関する世界最大のイベント「フラッシュメモリサミット(FMS:Flash Memory Summit)」が2020年11月10日〜12日に開催された。FMSは2019年まで、毎年8月上旬あるいは8月中旬に米国カリフォルニア州サンタクララで実施されてきた。COVID-19(新型コロナウイルス感染症)の世界的な大流行(パンデミック)による影響で、昨年(2020年)のFMS(FMS 2020)は開催時期が3カ月ほど延期されるとともに、バーチャルイベントとして開催された。

FMSは数多くの講演と、展示会で構成される。その中で、フラッシュメモリを含めた不揮発性メモリとストレージの動向に関するセッション「C-9: Flash Technology Advances Lead to New Storage Capabilities」が興味深かった。このセッションは4件の講演があり、その中でアナリストによる3件の講演が特に参考になったので、講演の概要をご紹介する。

なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

本シリーズの第10回から、技術調査会社TechInsightsでシニア技術フェローをつとめるJeodong Choe氏が「Technology Trend:NAND & Emerging Memory(NANDフラッシュメモリと次世代メモリの技術動向)」と題して講演した内容を説明してきた。第23回(前々回)は磁気抵抗メモリ(MRAM)をロジックLSIに埋め込む技術「eMRAM」の製品化事例を、第24回(前回)はフラッシュメモリをロジックLSIに埋め込む技術「eFLASH」の製品化事例をご報告した。

講演のアウトライン。3D NANDフラッシュの開発ロードマップと要素技術、次世代メモリと埋め込みメモリの開発ロードマップなどを解説する。出典:FMS 2020の講演「Technology Trend:NAND & Emerging Memory」の配布資料(クリックで拡大)

今回はDRAMをロジックLSIに埋め込む技術「eDRAM」の製品化事例を解説しよう。Choe氏は講演で、IBMとIntelによる製品化事例を紹介した。いずれもハイエンドのマイクロプロセッサでラストレベルキャッシュ(LLC)に採用されている。

IBMとIntelがハイエンドプロセッサに採用

キャッシュメモリには普通、SRAMが使われる。SRAMの製造プロセスはロジックLSIと変わらない。ロジックLSIの製造プロセスがまったく変更せずに使える。またSRAMは高速なメモリを作りやすい。ただし、記憶密度はDRAMやフラッシュメモリなどに比べるとはるかに低い。大容量のキャッシュを載せようとすると、シリコン面積が非常に大きくなり、製造コストを押し上げてしまう。

そこで大容量キャッシュ(普通はラストレベルキャッシュ)にはSRAMではなく、DRAMを使うことがある。DRAMの製造プロセスはロジックLSIと異なるので、そのままではロジックLSIに埋め込めない。埋め込みDRAM(eDRAM)では製造技術を改変してロジックLSI製造プロセスとの互換性をもたせる。単体のDRAMに比べると記憶密度は下がるものの、SRAMに比べると記憶密度はずっと高い。おおよそ3倍〜4倍の記憶密度が見込める。

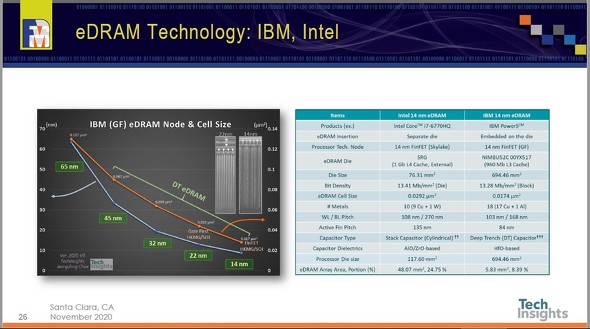

講演ではまず、IBMが開発してきたハイエンドプロセッサ向けeDRAMの歴史を振り返った。IBMのeDRAM技術はSOI CMOSプロセスと溝形キャパシタ(トレンチキャパシタ)を基本とする。メモリセル面積は65nm世代が0.127μm2、45nm世代が0.067μm2、32nm世代が0.039μm2、22nm世代が0.026μm2、14nm世代が0.0174μm2である。45nm世代のeDRAM技術は「Power7」プロセッサに、32nm世代のeDRAM技術は「Power7+」プロセッサに、22nm世代のeDRAM技術は「Power8」プロセッサに採用された。

埋め込みDRAM「eDRAM」の開発実績(左図)と製品化事例(右図)。左図の開発実績はIBMが開発してきたeDRAMのメモリセル面積と技術ノード。図面の右上はeDRAMセルの断面を電子顕微鏡で観察した画像。右図の製品化事例はIntelが開発した14nm世代のeDRAM技術(Core i7-6770HQなどに採用)と、IBMが開発した14nm世代のeDRAM技術(Power9に採用)。出典:FMS 2020の講演「Technology Trend:NAND & Emerging Memory」の配布資料(クリックで拡大)

それから、14nm世代のeDRAM技術を採用したハイエンドプロセッサ製品を2つ紹介した。1つはIntelが開発したSkylake世代のマイクロプロセッサである。14nm世代のバルクFinFETプロセスと互換の大容量eDRAMを開発した。記憶容量が1Gビットの4次キャッシュメモリとして働く。DRAMセルには積み上げ形キャパシタ(スタックドキャパシタ)を採用している。メモリセル面積は0.0292μm2。

もう1つはIBMが開発した「Power9」プロセッサである(参考記事:「IBM、「POWER9」でIntelに対抗」)。14nm世代のSOI FinFETプロセスと互換であり、記憶容量は960Mビット(120Mバイト)と大きい。3次のキャッシュメモリとして動作する。DRAMセルにはこれまでと同様に、溝形キャパシタ(トレンチキャパシタ)を採用した。メモリセル面積は0.0174μm2。

⇒「福田昭のストレージ通信」連載バックナンバー一覧

(次回に続く)

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

中国の3D NANDフラッシュメーカー「YMTC」の現状

中国の3D NANDフラッシュメーカー「YMTC」の現状

今回は、中国の3D NANDフラッシュベンチャーであるYMTC(Yangtze Memory Technologies Co., Ltd.)の現状に関する講演部分を紹介する。 高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

今回からは、半導体メモリのアナリストであるMark Webb氏の「Flash Memory Technologies and Costs Through 2025(フラッシュメモリの技術とコストを2025年まで展望する)」と題する講演の概要をご紹介する。 ソニーが20年度通期業績を上方修正、CMOSセンサーも想定上回る

ソニーが20年度通期業績を上方修正、CMOSセンサーも想定上回る

ソニーは2021年2月3日、2021年3月期(2020年度)第3四半期(2020年10〜12月期)決算を発表するとともに、2020年度通期業績予想を上方修正した。 前進し続けるIntel

前進し続けるIntel

Intelは2021年1月21日(米国時間)、業績発表を行った。それを見ると、同社の“終末時計”のカウントダウンに、少なくとも数秒は追加されたといえるだろう。ただし、完全に楽観視できるわけではなさそうだ。スピンドクター(情報操作が得意な人)たちは、Intelの2020年の業績のマイナス面だけを簡単に強調することができる。また、プラス面よりも欠点の方に反応を示す投資家たちもいる。 HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

今回は、米Western Digitalの2021会計年度第1四半期の業績を紹介する。 新材料で次々世代を狙う「強誘電体メモリ(FeRAM)」

新材料で次々世代を狙う「強誘電体メモリ(FeRAM)」

今回は「強誘電体メモリ(FeRAM)」を取り上げる。FeRAMの記憶原理と、60年以上に及ぶ開発の歴史を紹介しよう。