CMOSロジックの高密度化を後押しする次世代の電源配線技術:福田昭のデバイス通信(299) imecが語る3nm以降のCMOS技術(2)(1/2 ページ)

今回は、CMOSロジックの高密度化手法を簡単に解説する。

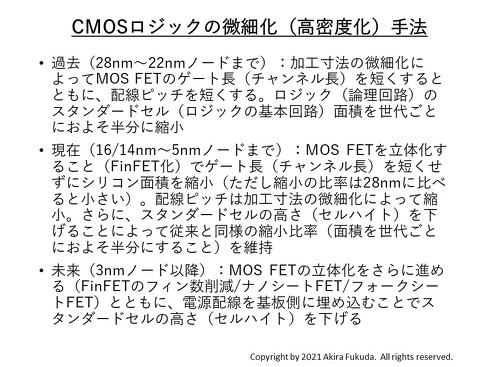

ロジック基本セルの縮小を支える要素技術が変貌

半導体のデバイス技術とプロセス技術に関する世界最大の国際学会「IEDM(International Electron Devices Meeting)」は、「チュートリアル(Tutorials)」と呼ぶ技術講座を本会議(技術講演会)とは別に、プレイベントとして開催してきた。2020年12月に開催されたIEDM(Covid-19の感染大流行によってバーチャルイベントとして開催)、通称「IEDM2020」では、合計で6本のチュートリアル講演が実施された。その中で「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials(CMOSを3nm以下に微細化する要素技術-デバイスアーキテクチャと寄生素子、材料)」が非常に興味深かった。講演者は研究開発機関のimecでTechnology Solutions and Enablement担当バイスプレジデントをつとめるMyung‐Hee Na氏である。

そこで本講座の概要を前回から、シリーズでお届けしている。なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

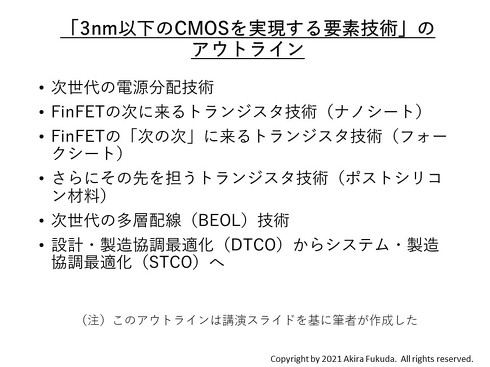

技術講座「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials(CMOSを3nm以下に微細化する要素技術-デバイスアーキテクチャと寄生素子、材料)」のアウトライン。講演スライド全体から筆者が作成したもの(クリックで拡大)

前回はCMOSロジック製造技術のロードマップを紹介するともに、トランジスタ技術やリソグラフィ技術などのトレンドを2025年まで予測した。今回は、CMOSロジックの高密度化手法を簡単に解説する。

過去、技術ノードで28nm世代までは、MOSFETのゲート長(チャンネル長)と配線のピッチを短くすることで、ロジックの基本セル(スタンダードセル)面積を世代ごとに約半分に縮小してきた。しかし22nm世代以降は、ゲート長(チャンネル長)をこれまで通りに短くすることが困難になった。短チャンネル効果によってMOSFETのしきい電圧がばらついてしまうことがその大きな要因である。

このため16/14nm世代からはMOSFETのチャンネルを立体化することで、チャンネル長を短くせずにMOSFETの寸法(シリコン基板表面と平行な方向の寸法)を小さくした。この立体チャンネルの代表がFinFET(フィンフェット)である。チャンネルとなるフィンのピッチを詰めることで、微細化を継続した。ただし従来の平面状MOSFETに比べると、寸法縮小の割合は小さくなった。このままでは、基本セルの面積を半分にはできない。

そこで基本セルの高さ(セルハイト)を低くすることで、基本セルの面積を前の世代の約半分に縮めた。セルハイトは、フィンと同じ方向(水平方向)に走る最下層金属配線(M0あるいはM1)の本数(トラック数)で決まる。例えば10トラック(10T)とは、1個の基本セルに10本の金属配線が含まれることを意味する。このトラック数を減らすとともに配線ピッチを短くすると、セルハイトを大幅に低くできる。16/14nm世代から5nm世代まではセルハイトを低くすることが、基本セルの面積縮小、すなわちCMOSロジックのトランジスタ密度向上に大きな役割を果たしてきた。

しかし配線のトラック数は、ある程度の数を確保することが欠かせない。金属配線は電源/接地線と信号線で構成される。いずれもCMOSロジックの基本セルに必須の回路素子である。

Copyright © ITmedia, Inc. All Rights Reserved.