™d¨Ι/êΎ£nêϋ²Χ•³²Ώçû²ί²≈âώ‰HÉuÉçÉbÉN²Χ™dà≥ç~âΚ²πîΦïΣà»âΚ²…£α¨Η¹Fïü™cèΚ²ΧÉfÉoÉCÉX£ êM¹i300¹j imec²Σ¨ξ²ι3nmà»ç~²ΧCMOS΄Zèp¹i3¹j¹i1/2 Éy¹[ÉW¹j

™d¨Ι¹^êΎ£nîzêϋ²πäνî¬ëΛ²…•³²Ώçû²ό¹uBPR¹iBuried Power Rails¹j¹v²…²¬²Δ²Ρâπêύ²Ζ²ι¹B

•³²Ώçû²ί™d¨Ι¹^êΎ£nêϋ²÷²Χ™d¨Ι΄ü΄΄éη•@

¹@îΦ™±ëΧ²ΧÉfÉoÉCÉX΄Zèp²ΤÉvÉçÉZÉX΄Zèp²…ä÷²Ζ²ιêΔäEç≈ëε²Χçëçέäwâο¹uIEDM¹iInternational Electron Devices Meeting¹j¹v²Ά¹A¹uÉ`ÉÖ¹[ÉgÉäÉAÉ΄¹iTutorials¹j¹v²Τ¨Ρ²‘΄Zèpçuçά²π•{âο΄c¹i΄Zèpçuâââο¹j²Τ²Άï ²…¹AÉvɨÉCÉxÉ™Ég²Τ²Β²ΡäJçΟ²Β²Ρ²Ϊ²Ϋ¹B2020îN12¨é²…äJçΟ²≥²ξ²ΫIEDM¹iCovid-19²ΧêΔäE™I²»½§çs²…²φ²Ν²ΡÉo¹[É`ÉÉÉ΄ÉCÉxÉ™Ég²Τ²Β²ΡäJçΟ¹j¹A£ èΧ¹uIEDM2020¹v²≈²Ά¹Aç΅¨v²≈6•{²ΧÉ`ÉÖ¹[ÉgÉäÉAÉ΄çuââ²Σéάé{²≥²ξ²Ϋ¹B²Μ²Χ£Ü²≈¹uInnovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials¹iCMOS²π3nmà»âΚ²…îςçΉâΜ²Ζ²ι½vëf΄Zèp-ÉfÉoÉCÉXÉA¹[ÉLÉeÉNÉ`ÉɲΤäώêΕëféq¹Açό½Ω¹j¹v²Σîώèμ²…΄Μ•Γê[²©²Ν²Ϋ¹Bçuââ铲Ά¨Λ΄ÜäJî≠΄@ä÷²Χimec²≈Technology Solutions and Enablement£S™•ÉoÉCÉXÉvɨÉWÉfÉ™Ég²π²¬²Τ²Ώ²ιMyung¹]Hee Naé¹²≈²†²ι¹B

¹@²Μ²±²≈•{çuçά²ΧäT½v²πëO¹Xâώ²©²γ¹AÉVÉä¹[ÉY²≈²®™Ά²·²Β²Ρ²Δ²ι¹B²»²®çuââ²Χ™ύ½e²Ψ²·²≈²Άêύ•Ψ²Σïsè\ïΣ²»²Τ²±²κ²Σ²†²ι²Χ²≈¹A•{ÉVÉä¹[ÉY²≈²Ά™«é“²Χ½ùâπ²πèï²·²ι²Ϋ²Ώ²…¹Açuââ²Χ™ύ½e²π™K΄X¹AïβëΪ²Β²Ρ²Δ²ι¹B²†²γ²©²Ε²Ώ²≤½Ιè≥²≥²ξ²Ϋ²Δ¹B

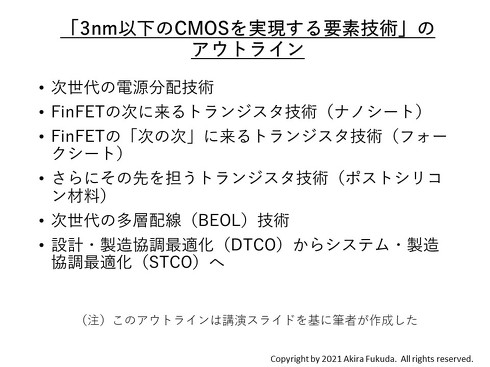

É`ÉÖ¹[ÉgÉäÉAÉ΄çuââ¹uInnovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials¹iCMOS²π3nmà»âΚ²…îςçΉâΜ²Ζ²ι½vëf΄Zèp-ÉfÉoÉCÉXÉA¹[ÉLÉeÉNÉ`ÉɲΤäώêΕëféq¹Açό½Ω¹j¹v²ΧÉAÉEÉgÉâÉCÉ™¹BçuââÉXÉâÉCÉhëSëΧ²©²γïM铲Σçλê§²Β²Ϋ²ύ²Χ¹iÉNÉäÉbÉN²≈ägëε¹j

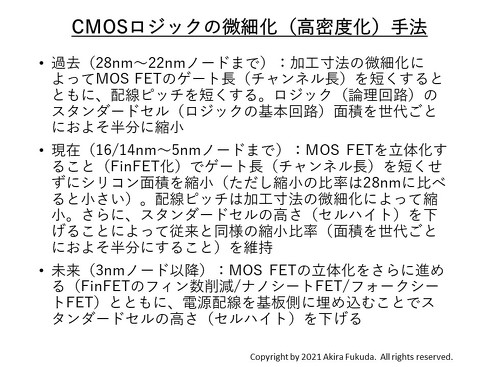

¹@ëO¹Xâώ²ΆCMOSÉçÉWÉbÉNêΜëΔ΄Zèp²ΧÉç¹[ÉhÉ}ÉbÉv²πè–âν²Ζ²ι²Τ²ύ²…¹AÉgÉâÉ™ÉWÉXÉ^΄Zèp²βÉäÉ\ÉOÉâÉtÉB΄Zèp²»²«²ΧÉgɨəÉh²π2025îN²ή²≈½\ëΣ²Β²Ϋ¹B²Μ²Β²ΡëOâώ²Ά¹ACMOSÉçÉWÉbÉN²Χ粕ߙxâΜéη•@²π代P²…êύ•Ψ²Β²Ϋ¹B16¹^14nmêΔëψà»ç~²Ά¹ACMOSÉçÉWÉbÉN²Χäν•{ÉZÉ΄¹iÉXÉ^É™É_¹[ÉhÉZÉ΄¹j²πèkè§²Ζ²ι²Ϋ²Ώ²…¹AÉZÉ΄²Χç²²≥¹iÉZÉ΄ÉnÉCÉg¹j²π£α²≠²Ζ²ι¹AMOSFET²ΧÉQ¹[ÉgÉsÉbÉ`²ΤÉtÉBÉ™ÉsÉbÉ`²π΄l²Ώ²ι¹A²Τ²Δ²Ν²Ϋéη•@²Σég²μ²ξ²Ρ²Ϊ²Ϋ¹B

¹@²±²Χ£Ü²≈éε½v²»éη£i²Σ¹AÉZÉ΄ÉnÉCÉg²Χ£α¨Η²≈²†²ι¹B΄οëΧ™I²…²Ά¹AÉtÉBÉ™²Τ™·²Εïϊ¨ϋ¹iêÖïΫïϊ¨ϋ¹j²…땲ιç≈âΚëw΄ύë°îzêϋ¹iM0²†²ι²Δ²ΆM1¹j²Χ•{êî¹iÉgÉâÉbÉNêî¹j²π¨Η²γ²Β²Ρ²Ϊ²Ϋ¹B

¹@²Ϋ²Ψ²Βîzêϋ²ΧÉgÉâÉbÉNêî²Ά¹A²†²ι£ω™x²Χêî²πämïέ²Ζ²ι²±²Τ²Σ¨΅²©²Ι²»²Δ¹B΄ύë°îzêϋ²Ά™d¨Ι¹^êΎ£nêϋ²ΤêMçÜêϋ²≈ç\꧲≥²ξ²ι¹B²Δ²Η²ξ²ύCMOSÉçÉWÉbÉN²Χäν•{ÉZÉ΄²…ïKê{²Χâώ‰Hëféq²≈²†²ι¹B5nmêΔëψ²ΧÉgÉâÉbÉNêî²Ά6•{¹i6ÉgÉâÉbÉN²†²ι²Δ²Ά6T¹j²≈²†²η¹AêMçÜêϋ²Σ4•{²Β²©²»²Δ¹BÉgÉâÉbÉNêî²π²≥²γ²…¨Η²γ²Ζ²±²Τ²ΣçΔ™ο²…²»²Ν²Ρ²Δ²Ϋ¹B²Μ²±²≈3nmêΔëψ²≈²Ά¹A™d¨Ι¹^êΎ£nêϋ²πäνî¬ëΛ²…•³²Ώçû²ό²±²Τ²≈¹AÉgÉâÉbÉNêî²π5•{²…¨Η²γ²Ζ²±²Τ²Σ£ώàΡ²≥²ξ²Ρ²Δ²ι¹BêMçÜêϋ²Χ•{êî²Ά4•{²≈²†²η¹A6ÉgÉâÉbÉN²Χäν•{ÉZÉ΄²Τ™·²ΕêMçÜêϋêî²πàέéù²Β²Ϋ¹B

Copyright © ITmedia, Inc. All Rights Reserved.