™d¨Ι/êΎ£nêϋ²Χ•³²Ώçû²ί²≈âώ‰HÉuÉçÉbÉN²Χ™dà≥ç~âΚ²πîΦïΣà»âΚ²…£α¨Η¹Fïü™cèΚ²ΧÉfÉoÉCÉX£ êM¹i300¹j imec²Σ¨ξ²ι3nmà»ç~²ΧCMOS΄Zèp¹i3¹j¹i2/2 Éy¹[ÉW¹j

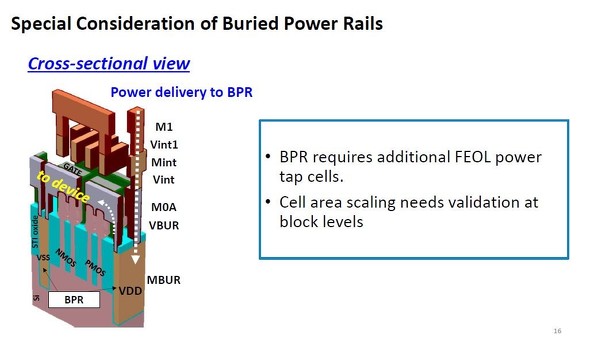

™d¨Ι¹^êΎ£nîzêϋ²πäνî¬ëΛ²…•³²Ώçû²ό¹uBPR¹iBuried Power Rails¹j¹v²…²¬²Δ²Ρâπêύ²Ζ²ι¹B

äν•{ÉZÉ΄²≈²Ά²»²≠¹Aâώ‰HÉuÉçÉbÉN²≈²Χ¨üèΊ²ΣïK½v

¹@Myung¹]Hee Naé¹²Άçuââ²≈¹A™d¨Ι¹^êΎ£nîzêϋ²πäνî¬ëΛ²…•³²Ώçû²ό΄Zèp¹iBPR¹FBuried Power Rails¹j²ΧçΧ½p²ΤFinFET²ΧÉtÉBÉ™êî²π¨Η²γ²Ζ²±²Τ²≈5ÉgÉâÉbÉN¹i5T¹j²Χäν•{ÉZÉ΄²πéά¨Μ²≈²Ϊ²ι²±²Τ²πéΠ²Β²Ϋ¹Bäν•{ÉZÉ΄²Χ£f• ç\ëΔ²ΆëOâώ²πéQèΤ²≥²ξ²Ϋ²Δ¹B

¹@BPR²π™±™ϋ²Ζ²ι²Τ¹Aäν•{ÉZÉ΄²Χç\ëΔ²Άè]½à²φ²η²ύ²Ά²ι²©²…ïΓéG²…²»²ι¹BÉgÉâÉ™ÉWÉXÉ^²Χèψ²…ɨÉCÉAÉEÉg²≥²ξ²Ϋ™d¨Ι¹^êΎ£n²Χîzêϋ¨Q¹iPDN¹FPower Delivery Network¹j²©²γ¹ABPR²…™d¨Ι²π΄ü΄΄²Β²»²·²ξ²Έ²»²γ²»²Δ²©²γ²Ψ¹B΄οëΧ™I²…²ΆPDN²Χîzêϋ¨Q²ΤBPR²π¨΄²‘²Ϋ²Ώ¹Aê²£Φïϊ¨ϋ²…ÉrÉA²β™d΄…ëw²»²«²Σ‰A²»²ιçΉ£Ζ²Δ£¨²Χ²φ²Λ²»ç\ëΔ²π¨`ê§²Ζ²ι¹B²±²Χç\ëΔ²π¨`ê§²Ζ²ιÉvÉçÉZÉX²Ά¹AÉgÉâÉ™ÉWÉXÉ^²ΧêΜëΔçH£ω¹iFEOL¹j²…£«âΝ²≥²ξ²ι¹B²ή²Ϋäν•{ÉZÉ΄²ΧÉVÉäÉRÉ™• ꜲπëùâΝ²≥²Ι²ι¹B

™d¨Ι¹^êΎ£nîzêϋ²πäνî¬ëΛ²…•³²Ώçû²ό΄Zèp¹iBPR¹FBuried Power Rails¹j²πçΧ½p²Β²ΫCMOSÉçÉWÉbÉNäν•{ÉZÉ΄²Χ£f• ç\ëΔ¹BBPR²…™d¨Ι²π΄ü΄΄²Ζ²ιç\ëΔ¹iî£²Δ•νàσ²ΧïîïΣ¹j²ΣïK½v²Τ²»²ι¹Bèo™T¹Fimec¹iIEDM2020²ΧÉ`ÉÖ¹[ÉgÉäÉAÉ΄çuââ¹uInnovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials¹v²Χîzïzéë½Ω¹j

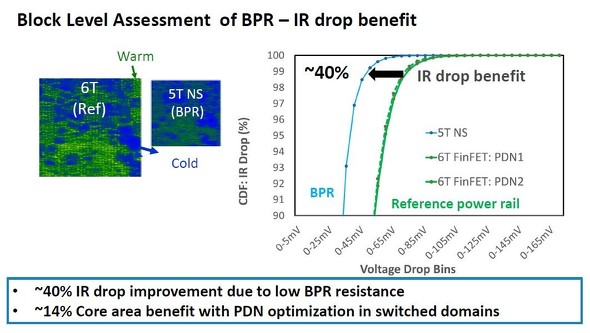

¹@²±²Χ²Ϋ²ΏBPR²Χâe΄Ω²Άäν•{ÉZÉ΄²≈²Ά²»²≠¹Aâώ‰HÉuÉçÉbÉN²≈¨üèΊ²Ζ²ιïK½v²Σ²†²ι²Τ²Ζ²ι¹Béάçέ²…6ÉgÉâÉbÉN¹i6T¹j²Χâώ‰HÉuÉçÉbÉN²Τ5ÉgÉâÉbÉN¹i5T¹j²Χâώ‰HÉuÉçÉbÉN²≈¨üèΊ²Β²Ρ²ί²Ι²Ϋ¹B6T²ΆFinFET²Χäν•{ÉZÉ΄¹A5T²ΆÉiÉmÉV¹[Ég¹iNS¹jFET²ΤBPR²Χäν•{ÉZÉ΄²≈²†²ι¹B

¹@BPR²π™±™ϋ²Ζ²ι²±²Τ²…²φ²Ν²Ρ¹A™d¨Ι¹^êΎ£nîzêϋ²…²φ²ι™dà≥ç~âΚ²Ά•ώ40¹™¨Η²Τëεïù²…觲≥²≠²»²Ν²Ϋ¹BBPR²Άîzêϋ²πçΉ²≠²Β²Ρ²ύç²²≥²πämïέ²≈²Ϊ²ι²Χ²≈¹Aîzêϋ²Χ£f• Ꜳπëε²Ϊ²≠²Β²β²Ζ²Δ¹B²Ζ²»²μ²Ω™d΄C£οçR²π£α²≠²≈²Ϊ²ι¹BBPR²Χ£α²Δ£οçR²Σ¹A™dà≥ç~âΚ²Χ£α¨Η¹i™d¨Ι™dà≥²Χàά£ηâΜ¹j²…ëε²Ϊ²≠äώ½^²Β²Ϋ¹B

¹@²≥²γ²…¹A™d¨Ι΄ü΄΄îzêϋ¨Q¹iPDN¹j²πç≈™KâΜ²Ζ²ι²±²Τ²≈¹Aâώ‰HÉuÉçÉbÉN²ΧÉVÉäÉRÉ™• Ꜳπ•ώ14¹™¨Η²Τ觲≥²≠²≈²Ϊ²Ϋ¹iÉgÉâÉ™ÉWÉXÉ^²Χèk觲ΤîzêϋÉgÉâÉbÉNêî²Χ¨Ηè≠²…²φ²ιÉVÉäÉRÉ™• ꜲΧçμ¨ΗïΣ²Άè€²≠¹j¹B

âώ‰HÉuÉçÉbÉN²≈BPR²Χ¨χâ ²π¨üèΊ²Β²Ϋ¨΄â ¹BçΕ²Άâώ‰HÉuÉçÉbÉN²Χëε²Ϊ²≥²ΤâΖ™xïΣïz²Χîδär¹BBPR²πçΧ½p²Β²Ϋ5T¹i5ÉgÉâÉbÉN¹jÉZÉ΄²Χâώ‰HÉuÉçÉbÉN²≈²Ά¹AâΖ™x²Χç²²ΔïîïΣ¹iWarm¹j²Σ²β²β觲≥²≠²»²Ν²Ρ²Δ²ι¹BâE²Ά™dà≥ç~âΚ¹iIRÉhÉçÉbÉv¹j²Χ½ίêœïΣïz²πîδär²Β²ΫÉOÉâÉt¹BBPR²π™±™ϋ²Β²Ϋ5TÉZÉ΄²Χâώ‰HÉuÉçÉbÉN²≈²Ά¹A™dà≥ç~âΚ²π•ώ40¹™¨Η²Τëεïù²…£α²≠²≈²Ϊ²Ϋ¹Bèo™T¹Fimec¹iIEDM2020²ΧÉ`ÉÖ¹[ÉgÉäÉAÉ΄çuââ¹uInnovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials¹v²Χîzïzéë½Ω¹j

¹iéüâώ²…ë±²≠¹j

¹Υ¹uïü™cèΚ²ΧÉfÉoÉCÉX£ êM¹v‰AçΎÉoÉbÉNÉiÉ™Éo¹[àξ½½

Copyright © ITmedia, Inc. All Rights Reserved.

ä÷‰A΄Lé•

£Üçë²Χ3D NANDÉtÉâÉbÉVÉÖɹ¹[ÉJ¹[¹uYMTC¹v²Χ¨Μèσ

£Üçë²Χ3D NANDÉtÉâÉbÉVÉÖɹ¹[ÉJ¹[¹uYMTC¹v²Χ¨Μèσ

çΓâώ²Ά¹A£Üçë²Χ3D NANDÉtÉâÉbÉVÉÖÉxÉ™É`Éɹ[²≈²†²ιYMTC¹iYangtze Memory Technologies Co., Ltd.¹j²Χ¨Μèσ²…ä÷²Ζ²ιçuââïîïΣ²πè–âν²Ζ²ι¹B ç²ëwâΜ²Χ¨pë±²≈¹AêΜëΔÉRÉXÉg²πîöâΚ²Α²Ζ²ι3D NANDÉtÉâÉbÉVÉÖ

ç²ëwâΜ²Χ¨pë±²≈¹AêΜëΔÉRÉXÉg²πîöâΚ²Α²Ζ²ι3D NANDÉtÉâÉbÉVÉÖ

çΓâώ²©²γ²Ά¹AîΦ™±ëΧɹɲÉä²ΧÉAÉiÉäÉXÉg²≈²†²ιMark Webbé¹²Χ¹uFlash Memory Technologies and Costs Through 2025¹iÉtÉâÉbÉVÉÖɹɲÉä²Χ΄Zèp²ΤÉRÉXÉg²π2025îN²ή²≈™W•]²Ζ²ι¹j¹v²Τëη²Ζ²ιçuââ²ΧäT½v²π²≤è–âν²Ζ²ι¹B É\Éj¹[²Σ20îN™x£ äζ΄Τê―²πèψïϊèCê≥¹ACMOSÉZÉ™ÉT¹[²ύëz£ηèψâώ²ι

É\Éj¹[²Σ20îN™x£ äζ΄Τê―²πèψïϊèCê≥¹ACMOSÉZÉ™ÉT¹[²ύëz£ηèψâώ²ι

É\Éj¹[²Ά2021îN2¨é3™ζ¹A2021îN3¨éäζ¹i2020îN™x¹jëφ3élîΦäζ¹i2020îN10¹`12¨éäζ¹j¨àéZ²πî≠ï\²Ζ²ι²Τ²Τ²ύ²…¹A2020îN™x£ äζ΄Τê―½\ëz²πèψïϊèCê≥²Β²Ϋ¹B ëOêi²Βë±²·²ιIntel

ëOêi²Βë±²·²ιIntel

Intel²Ά2021îN1¨é21™ζ¹iïΡçëéû䑹j¹A΄Τê―î≠ï\²πçs²Ν²Ϋ¹B²Μ²ξ²π¨©²ι²Τ¹A™·é–²Χ¹gèI••éû¨v¹h²ΧÉJÉEÉ™ÉgÉ_ÉEÉ™²…¹Aè≠²»²≠²Τ²ύêîïb²Ά£«âΝ²≥²ξ²Ϋ²Τ²Δ²Π²ι²Ψ²κ²Λ¹B²Ϋ²Ψ²Β¹Aä°ëS²…äyäœé΄²≈²Ϊ²ι²μ²·²≈²Ά²»²≥²Μ²Λ²Ψ¹BÉXÉsÉ™ÉhÉNÉ^¹[¹ièνïώëÄçλ²Σ™Ψà”²»êl¹j²Ϋ²Ω²Ά¹AIntel²Χ2020îN²Χ΄Τê―²ΧÉ}ÉCÉiÉX• ²Ψ²·²π代P²…΄≠£≤²Ζ²ι²±²Τ²Σ²≈²Ϊ²ι¹B²ή²Ϋ¹AÉvÉâÉX• ²φ²η²ύ¨΅™_²Χïϊ²…îΫâû²πéΠ²Ζ™äéëâΤ²Ϋ²Ω²ύ²Δ²ι¹B HDDëεéηWestern Digital²Χ΄Τê―¹AëOîN™·äζîδ²Χâc΄Τ½‰âv²Σ3élîΦäζ‰Aë±²≈ëùâΝ

HDDëεéηWestern Digital²Χ΄Τê―¹AëOîN™·äζîδ²Χâc΄Τ½‰âv²Σ3élîΦäζ‰Aë±²≈ëùâΝ

çΓâώ²Ά¹AïΡWestern Digital²Χ2021âο¨vîN™xëφ1élîΦäζ²Χ΄Τê―²πè–âν²Ζ²ι¹B êVçό½Ω²≈éü¹XêΔëψ²πë_²Λ¹u΄≠½U™dëΧɹɲÉä¹iFeRAM¹j¹v

êVçό½Ω²≈éü¹XêΔëψ²πë_²Λ¹u΄≠½U™dëΧɹɲÉä¹iFeRAM¹j¹v

çΓâώ²Ά¹u΄≠½U™dëΧɹɲÉä¹iFeRAM¹j¹v²πéφ²ηèψ²Α²ι¹BFeRAM²Χ΄Lâ·¨¥½ù²Τ¹A60îNà»èψ²…΄y²‘äJî≠²Χ½πéj²πè–âν²Β²φ²Λ¹B