FinFETの実用化で必須となった「設計・製造協調最適化(DTCO)」:福田昭のデバイス通信(325) imecが語る3nm以降のCMOS技術(28)(1/2 ページ)

今回から、「設計・製造協調最適化(DTCO)からシステム・製造協調最適化(STCO)へ」の講演概要を説明する。

微細化と基本セル縮小の両方でシリコン面積を削減

半導体のデバイス技術とプロセス技術に関する世界最大の国際学会「IEDM(International Electron Devices Meeting)」は、「チュートリアル(Tutorials)」と呼ぶ技術講座を本会議(技術講演会)とは別に、プレイベントとして開催してきた。2020年12月に開催されたIEDM(Covid-19の世界的な流行によってバーチャルイベントとして開催)、通称「IEDM2020」では、合計で6本のチュートリアル講演が実施された。その中で「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials(CMOSを3nm以下に微細化する要素技術-デバイスアーキテクチャと寄生素子、材料)」が非常に興味深かった。講演者は研究開発機関のimecでTechnology Solutions and Enablement担当バイスプレジデントをつとめるMyung‐Hee Na氏である。

そこで本講座の概要を本コラムの第298回から、シリーズでお届けしている。なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

チュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials(CMOSを3nm以下に微細化する要素技術-デバイスアーキテクチャと寄生素子、材料)」のアウトライン。講演スライド全体から筆者が作成したもの。今回から、「設計・製造協調最適化(DTCO)からシステム・製造協調最適化(STCO)へ」の講演パートを紹介する[クリックで拡大]

本シリーズの第21回から第27回(前回)までは、5番目のパートである「次世代の多層配線(BEOL)技術」の講演内容を紹介してきた。今回からは、6番目(最後)のパートである「設計・製造協調最適化(DTCO)からシステム・製造協調最適化(STCO)へ」の講演概要を説明する。

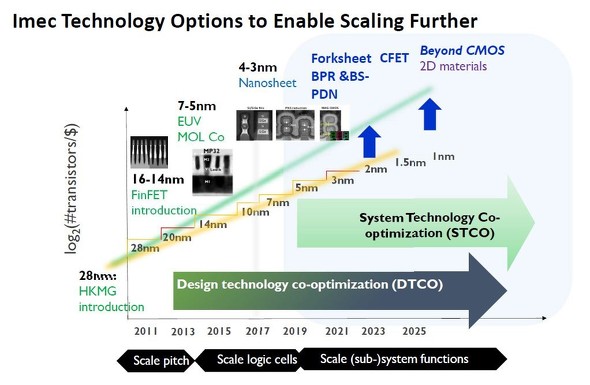

CMOSロジックの技術ロードマップ[クリックで拡大] 出所:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料)

本シリーズでこれまで述べてきたように、3nm以降のCMOSロジックを構成する要素技術は、5nm以前とは大きく変わる可能性がある。電源分配技術、トランジスタ技術、多層配線技術のいずれもが、新たな要素技術の開発によって3nmノードから2.5nmノード、2nmノード、1.5nmノード、1.0nmノードへと続くスケーリングを促す。

これらの要素技術を活用するときに不可欠なのが、トランジスタ寸法や配線ピッチなどの微細化になるべく頼らずに、スケーリング(高密度化)を促す手法である。具体的には微細化と併用して、CMOSロジックの基本セル(スタンダードセル)を縮小することによって論理回路のシリコン面積を従来と同様の比率で削減する。その重要な手段が「設計・製造協調最適化(DTCO:Design Technology Co-Optimization)」と呼ばれる、「消費電力と性能、シリコン面積(PPA:Power、Performance、Area)」のバランスをレイアウト設計の段階で最適化する技術である。16/14nm以降のCMOSロジック設計では、必須の技術だと言える。

Copyright © ITmedia, Inc. All Rights Reserved.