FinFETの実用化で必須となった「設計・製造協調最適化(DTCO)」:福田昭のデバイス通信(325) imecが語る3nm以降のCMOS技術(28)(2/2 ページ)

今回から、「設計・製造協調最適化(DTCO)からシステム・製造協調最適化(STCO)へ」の講演概要を説明する。

PPAが最適になるような設計ルールとプロセス条件を見つけ出す

DTCOが必須となった大きな理由は、デバイスの3次元化である。具体的には、22nm/16nm世代のCMOSロジックでFinFET(フィンフェット)を導入したことによる。それまでのプレーナー型MOSFETではゲートおよびチャンネルの平面的な寸法を詰めること(加工寸法の短縮)が高密度化の主な手法だった。しかしFinFETではゲート(およびチャンネル)はあまり短くならない。フィンの寸法(幅と高さ、ピッチ)、それから最下層付近の金属配線ピッチがトランジスタの密度を左右する。

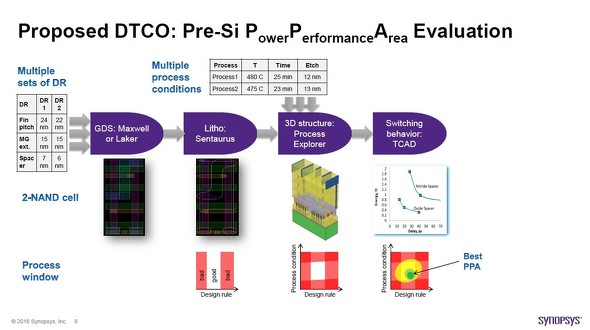

加工寸法(設計ルール)の短縮だけでなく、新たな要素技術を追加することよってトランジスタ密度を高め、その効果をレイアウト設計の段階で確認する必要が生じた。設計ルール(DR:Design Rule)とプロセス条件の2つのプロセス・ウインドウから、「消費電力と性能、シリコン面積(PPA:Power、Performance、Area)」のバランスが最適となるポイント(条件)をシミュレーションによって探索する。

設計・製造協調最適化(DTCO:Design Technology Co-Optimization)の例。設計ルールとプロセス条件のウインドウから、シミュレータ「TCAD」によってPPAが最適になるポイントを見つける[クリックで拡大] 出所:Synopsysが2016年7月に展示会兼講演会「SEMICON West 2016」で「Design-Technology Co-Optimization for 5nm Node and Beyond(5nm以降の世代における設計と製造の最適化)」と題して講演した資料

CMOSロジックの微細化と複雑化が最適化を難しくする

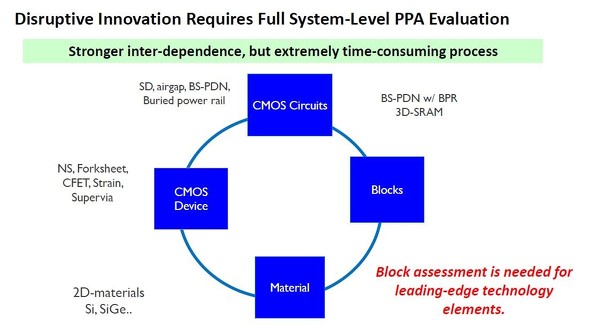

最先端のCMOSロジックは数多くの要素技術によって構成されている。採用する要素技術は、技術ノードの進化とともに増加していく。トランジスタ材料ではシリコンとゲルマニウムが既に使われている。将来は化合物半導体や2次元材料などが加わる可能性がある。トランジスタ技術ではナノシート構造やフォークシート構造、さらにはコンプリメンタリ構造が将来の候補となっている。トランジスタ間を相互接続する回路だと、ルテニウム配線やスーパービア、埋め込み電源/接地配線、埋め込み電源分配などの要素技術が控える。回路ブロックやマクロセルなどのサブシステムでは、2.5次元集積化技術と3次元集積化技術が導入されつつある。

3nm以降のCMOSロジックを構成する階層と新たな要素技術群。新たな要素技術群は製造に時間がかかるとともに、相互に影響し合う[クリックで拡大] 出所:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料)

これらの要素技術はお互いに影響し合う。5nm以降の技術ノードでは、基本セルよりも大規模な回路ブロックでPPAの最適化をあらかじめ詰めておく必要がある。この新たな最適化を支えるのが「システム・製造協調最適化(STCO:System Technology Co-Optimization)」と呼ばれる手法だ。詳しくは次回に述べたい。

(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

2層上下の配線層をダイレクトに接続する「スーパービア」の課題(後編)

2層上下の配線層をダイレクトに接続する「スーパービア」の課題(後編)

後編となる今回は、1本のスーパービアがブロックするトラック数を減らしたときに生じる問題と、その解決策を述べる。 高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

今回からは、半導体メモリのアナリストであるMark Webb氏の「Flash Memory Technologies and Costs Through 2025(フラッシュメモリの技術とコストを2025年まで展望する)」と題する講演の概要をご紹介する。 埋め込みDRAMが大容量キャッシュの製造コスト低減に貢献

埋め込みDRAMが大容量キャッシュの製造コスト低減に貢献

今回はDRAMをロジックLSIに埋め込む技術「eDRAM」の製品化事例を解説する。 前進し続けるIntel

前進し続けるIntel

Intelは2021年1月21日(米国時間)、業績発表を行った。それを見ると、同社の“終末時計”のカウントダウンに、少なくとも数秒は追加されたといえるだろう。ただし、完全に楽観視できるわけではなさそうだ。スピンドクター(情報操作が得意な人)たちは、Intelの2020年の業績のマイナス面だけを簡単に強調することができる。また、プラス面よりも欠点の方に反応を示す投資家たちもいる。 HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

今回は、米Western Digitalの2021会計年度第1四半期の業績を紹介する。 新材料で次々世代を狙う「強誘電体メモリ(FeRAM)」

新材料で次々世代を狙う「強誘電体メモリ(FeRAM)」

今回は「強誘電体メモリ(FeRAM)」を取り上げる。FeRAMの記憶原理と、60年以上に及ぶ開発の歴史を紹介しよう。