3nm以降のCMOSロジックを支える多層配線技術:福田昭のデバイス通信(318) imecが語る3nm以降のCMOS技術(21)(1/2 ページ)

「IEDM2020」の講演内容を紹介するシリーズ。今回から、「次世代の多層配線(BEOL)技術」の講演内容を紹介していく。

5nmノード以降は多層配線の微細化ペースが大幅に鈍化

半導体のデバイス技術とプロセス技術に関する世界最大の国際学会「IEDM(International Electron Devices Meeting)」は、「チュートリアル(Tutorials)」と呼ぶ技術講座を本会議(技術講演会)とは別に、プレイベントとして開催してきた。2020年12月に開催されたIEDM(Covid-19の世界的な流行によってバーチャルイベントとして開催)、通称「IEDM2020」では、合計で6本のチュートリアル講演が実施された。その中で「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials(CMOSを3nm以下に微細化する要素技術-デバイスアーキテクチャと寄生素子、材料)」が非常に興味深かった。講演者は研究開発機関のimecでTechnology Solutions and Enablement担当バイスプレジデントをつとめるMyung‐Hee Na氏である。

そこで本講座の概要を本コラムの第298回から、シリーズでお届けしている。なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

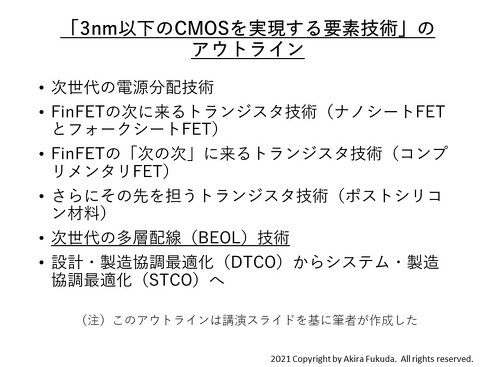

チュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials(CMOSを3nm以下に微細化する要素技術-デバイスアーキテクチャと寄生素子、材料)」のアウトライン。講演スライド全体から筆者が作成したもの。今回から、「次世代の多層配線(BEOL)技術」の講演パートを紹介する(クリックで拡大)

前々回と前回は、4番目のパートである「さらにその先を担うトランジスタ技術(ポストシリコン材料)」の講演部分を報告した。具体的には、2次元(2D)材料の「遷移金属ダイカルコゲナイド(TMD)」をチャンネルに採用することにより、1nm以下(サブナノメートル)の技術ノードを目指す。

今回からは、5番目のパートである「次世代の多層配線(BEOL)技術」の講演内容を紹介していく。3nm以降の技術世代(技術ノード)を担う、多層配線(BEOL)技術が主題となる。始めは配線の微細化ロードマップを示そう。

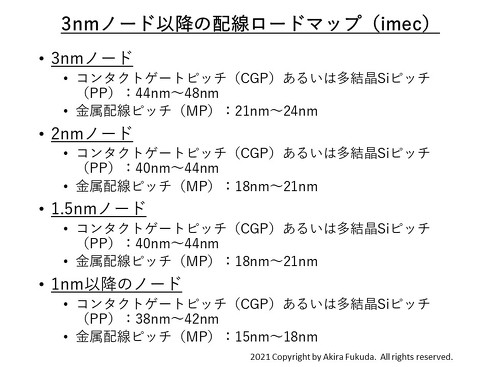

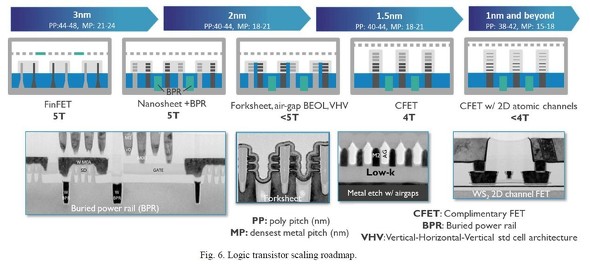

3nm以降のCMOSロジックの技術ロードマップ。出典:imec(IEDM2020のキーノート講演「Future Logic Scaling: Towards Atomic Channels and Deconstructed Chips」の論文資料) (クリックで拡大)

多層配線を構成する金属配線の最小ピッチ(MP)は、5nmノードが28nm、3nmノードが21nm、2nmノードが16nmというのが3年ほど前のロードマップだった。またコンタクトゲートピッチ(CGP)は、5nmノードが48nm、3nmノードが45nm、2nmノードが42nmとなっていた。

それが最新のロードマップでは、金属配線の微細化が鈍化しつつある。3nmノードのMPは21nm〜24nm、CGP(あるいはPP)は44nm〜48nmである。2nmノードと1.5nmノードのMPは18nm〜21nm、CGPは40nm〜44nm、1.0nm以下のノードだとMPが15nm〜18nm、CGPは38〜42nmとなる。金属配線ピッチ(MP)の微細化世代は以前のロードマップでは21nmの次が16nmだった。それが最新のロードマップは21nmの次が18nm、その次が15nmと緩やかになっている。

Copyright © ITmedia, Inc. All Rights Reserved.