SiC-MOSFETの性能が6〜80倍に、トレンチ型に応用可能:界面の欠陥低減と平たん性向上で(1/3 ページ)

京都大学 大学院 工学研究科の木本恒暢教授、立木馨大博士後期課程学生らのグループは2021年10月27日、SiC半導体の課題である界面の欠陥を大幅に削減し、SiC-MOSFETの性能を6〜80倍に向上することに成功したと発表した。

京都大学 大学院 工学研究科の木本恒暢教授、立木馨大博士後期課程学生らのグループは2021年10月27日、SiC半導体の課題である界面の欠陥を大幅に削減し、SiC-MOSFETの性能を6〜80倍に向上することに成功したと発表した。

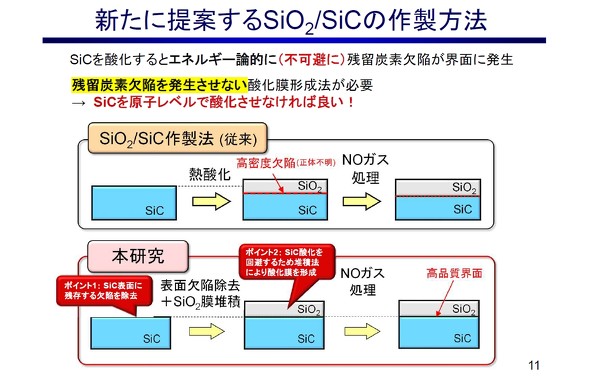

次世代パワー半導体の“代表格”ともいえるSiCパワーデバイスでは長らく、界面に発生する欠陥(界面欠陥)が大きな課題となっていた。具体的には、SiC-MOSFETにおいてSiCと酸化膜(SiO2)の接合界面に多数存在する欠陥のことだ。SiC/SiO2の界面に存在する欠陥は、Si/SiO2の約100倍。この欠陥により電子移動度が小さくなり、それがSiC-MOSFETが本来持つ性能の発揮を阻んでいた。

大きなブレークスルーがあったのは2020年8月。京都大学と東京工業大学が、欠陥の正体を突き止め、欠陥の発生を最小限に抑える独自のSiO2膜生成手法(以下、独自手法とする)を発表したのだ。これにより、界面欠陥を従来の10分の1にまで低減し、オン抵抗を減らしてSiC-MOSFETを高性能化することに成功した。

そして今回、京都大学は、その独自手法を用いて、SiC-MOSFETの新たな高性能化を発表した。

性能向上の鍵は「トレンチの側壁」

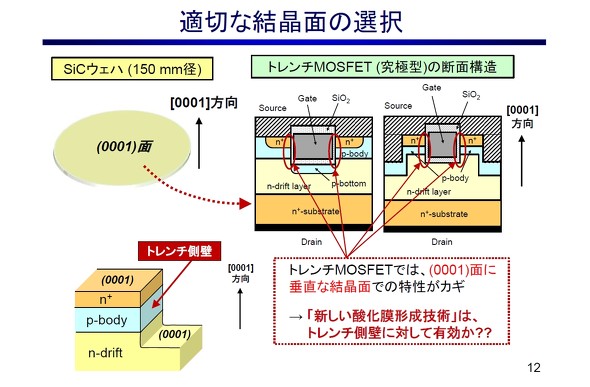

今回、木本氏らが評価の対象としたのは、トレンチ型SiC-MOSFETの“トレンチ側壁”である。2020年8月の発表は、SiCウエハーの表面((0001)面)に酸化膜を生成して評価した結果だった。発表後、「独自手法はトレンチ側壁に対しても有効なのかという問い合わせを数多くもらった」(木本氏)ものの、その時点ではデータを取ることができなかった。「トレンチ側壁」に相当する試料を準備していなかったからだ。

トレンチ型SiC-MOSFETは、SiCトランジスタの究極的な高性能化において最も有望な素子とされる。実際、SiC-MOSFETを手掛けるメーカーの多くが、トレンチ型を採用している。このトレンチ型SiC-MOSFETでは、SiC/SiO2界面がトレンチの側壁に形成される。つまり、この側壁で良い特性を得られるかがどうかが、トレンチ型SiC-MOSFETの高性能化で肝となってくるのだ。

SiCの結晶では、「Si面」と呼ばれる(0001)面に対して垂直な面は「A面」と「M面」があり、トレンチ側壁となるのは、このA面かM面である。「どちらをトレンチ側壁にしてもよいが、最近ではM面の方が筋がよいとされ、M面を側壁とするメーカーも増えている」と木本氏は説明する。

Copyright © ITmedia, Inc. All Rights Reserved.