SiC-MOSFETの性能が6〜80倍に、トレンチ型に応用可能:界面の欠陥低減と平たん性向上で(2/3 ページ)

京都大学 大学院 工学研究科の木本恒暢教授、立木馨大博士後期課程学生らのグループは2021年10月27日、SiC半導体の課題である界面の欠陥を大幅に削減し、SiC-MOSFETの性能を6〜80倍に向上することに成功したと発表した。

“つるつる”の界面

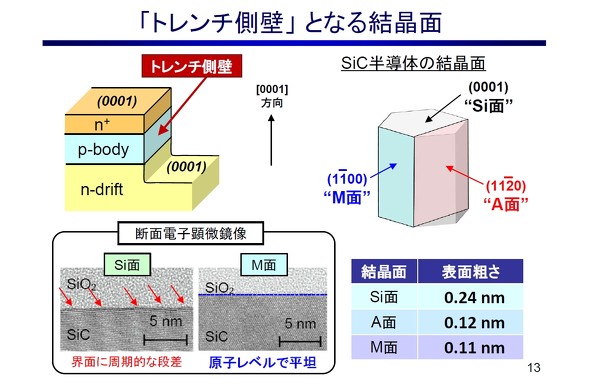

まずSi面/A面/M面上に結晶を成長させて独自手法で酸化膜を形成し、界面の断面を電子顕微鏡で確認すると、表面の粗さがかなり異なることが分かった。Si面では、SiC/SiO2の界面に原子レベルの段差が周期的に存在するが、A面とM面の界面は原子レベルで平たんになっている。

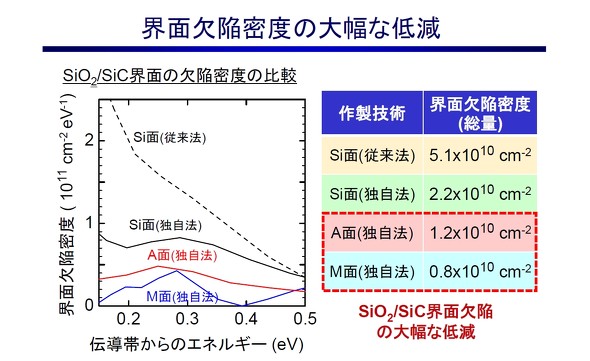

さらに界面欠陥密度を調べると、Si面では2.2×1010cm-2だったものが、A面では1.2×1010cm-2、M面では0.8×1010cm-2と、大幅に低減していることが明らかになった。

「Si面で独自手法が有効だったからといって、A面やM面でもうまくいくという保証は全くなかった。結晶の面が異なれば振る舞いも異なるというのは半導体の常識であり、(結果を得るまで)本当に怖かった」と木本氏は語る。結果は、期待以上のものだった。

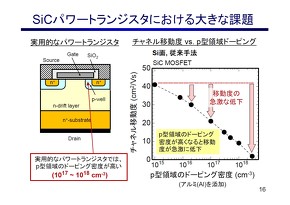

プレーナ型SiC-MOSFETでチャネル移動度が6〜80倍に

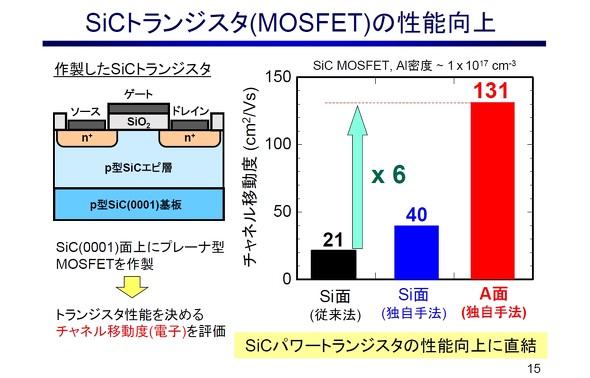

SiC-MOSFETの性能も大幅に上がった。木本氏らは、

- 従来手法で酸化膜を生成したSi面(従来法+Si面)

- 独自手法で酸化膜を生成したSi面(独自手法+Si面)

- 独自手法で酸化膜を生成したA面(独自手法+A面)

- 独自手法で酸化膜を生成したM面(独自手法+M面)

という4つの基板を用意し、それらの基板上にプレーナ型MOSFET(トレンチ型ではないことに注意)を作成してチャネル移動度を評価。その結果、独自手法+A面上に作成したSiC-MOSFETのチャネル移動度は131cm2/Vsと、従来法+Si面に比べて6倍以上の数値となった。独自手法+Si面に比べても3倍以上となっている。

独自手法+A面では、チャネル移動度が従来法+Si面の6倍以上と大幅に向上した。グラフには表示されていないが、独自手法+M面の結果は約110cm2/Vsだという。なお、左のプレーナ型MOSFETは、Si面上に作成した場合の例。今回の評価では、Si面の他に、A面とM面上にもMOSFETを作成した[クリックで拡大] 出所:京都大学

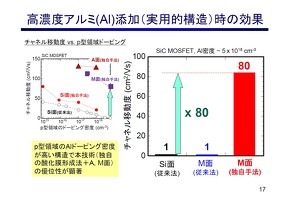

なお、実際に製造されるSiCトランジスタ同様、高濃度に不純物(アルミニウム)を添加したp型SiCを用いてA面、M面上にMOSFETを作成した結果、従来法によるA面、M面上のMOSFETに比べ、6〜80倍の性能向上を達成した。

Copyright © ITmedia, Inc. All Rights Reserved.