¹uCoWoS¹v²ΧïWèÄÉA¹[ÉLÉeÉNÉ`ÉÉ²Σ¨Ύ΄q²…²φ²ιäJî≠äζ䑲π£Zèk¹Fïü™cèΚ²ΧÉfÉoÉCÉX£ êM¹i336¹j TSMC²ΣäJî≠²Β²Ρ²Ϊ²Ϋç≈êφ£[ÉpÉbÉP¹[ÉWÉ™ÉO΄Zèp¹i9¹j¹i2/2 Éy¹[ÉW¹j

çΓâώ²Ά¹uCoWoS¹v²ΧïWèÄéd½l²…²¬²Δ²Ρâπêύ²Ζ²ι¹B¹y£υê≥²†²η¹z

çLë―àφɹɲÉä¹uHBM¹v²ΤSoC²πç§çΎ²Ζ²ι¹uCoWoS_S¹v²Χç\꧲ΤɨÉCÉAÉEÉg²πïWèÄâΜ

¹@¹uCoWoS_S¹v²Χé彧²Ά¹AçLë―àφɹɲÉäɲÉWÉÖ¹[É΄¹uHBM¹iHigh Bandwidth Memory¹j¹v²Τëε΄K•Ά²»SoC²πç§çΎ²Β²Ϋç²êΪî\ÉTÉuÉVÉXÉeÉIJ≈²†²ι¹BSiÉCÉ™É^¹[É|¹[ÉU²πâν²Β²ΡHBM²ΤSoC²πêΎë±²Ζ²ι²±²Τ²≈¹AçLë―àφ²ΧɹɲÉäÉAÉNÉZÉX²πéά¨Μ²Ζ²ι¹B

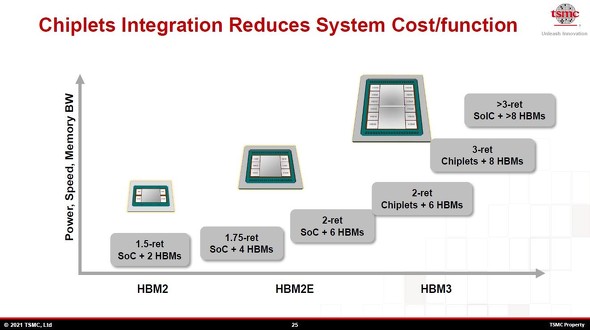

¹@¹uHBM¹v²Χéd½l²ΆêΔëψ²≤²Τ²…΄Λ£ ΄Käi²Σ£η²Ώ²γ²ξ²Ρ²Δ²ι¹BêΜïi²÷²Χï¹΄y²Άëφ2êΔëψ²Χ¹uHBM2¹v²©²γén²ή²Ν²Ϋ¹Béü²ΧêΔëψ²ΆHBM2²Χ΄≠âΜî≈¹uHBM2E¹v²≈²†²ι¹B²≥²γ²…éü²ΧêΔëψ²Ά¹uHBM3¹v²≈¹Aëε½e½ âΜ²ΤçLë―àφâΜ²Σêi²ό¹BâΝ²Π²Ρ¹uCoWoS_S¹v²…™΄çΎ²Ζ²ιHBM²Χêî½ ²ΆëùâΝ²Β¹ASiÉCÉ™É^¹[É|¹[ÉU²Χ• ꜲΆägëε²Β¹ASoC²ΧêΜëΔ΄Zèp²ΆîςçΉâΜ²Ζ²ι¹BSoC²ΆÉVÉ™ÉOÉ΄É_ÉC²©²γÉ`ÉbÉvɨÉbÉg¹A²≥²γ²…²ΆSoIC¹iSystem on Integrated Chips¹j²÷²Τ¨`둲πïœ²Π²ι¹B¹uCoWoS_S¹v²πç\ê§²Ζ²ι½vëf΄Zèp²ΆëùâΝ²Β¹A²©²¬ïΓéG²…²»²ι¹B

çLë―àφɹɲÉäɲÉWÉÖ¹[É΄¹uHBM¹v²ΧêiâΜ¹iâΓé≤¹j²Τ¹AëΈâû²Ζ²ι¹uCoWoS_S¹v²ΧèΝîο™d½Ά¹A맙x¹AɹɲÉäë―àφ²Χê³àΎ¹iècé≤¹j¹mÉNÉäÉbÉN²≈ägëε¹n èoèä¹FTSMC¹iHot Chips 33²Χçuââ¹uTSMC packaging technologies for chiplets and 3D¹v²ΧÉXÉâÉCÉh²©²γ¹j

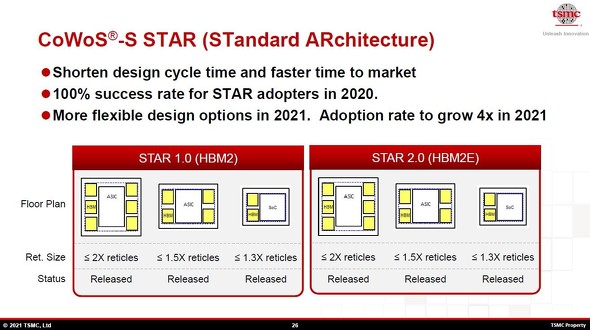

¹@²Μ²±²≈TSMC²Ά¹A¨Ύ΄q²≈²†²ιîΦ™±ëΧÉxÉ™É_¹[²Σ¹uCoWoS_S¹v²πçΧ½p²Β²ΫÉTÉuÉVÉXÉeÉIJπëfë¹²≠äJî≠²≈²Ϊ²ι²φ²Λ²…¹Aç\꧲ΤɨÉCÉAÉEÉg²πïWèÄâΜ²Β²Ϋ¹uCoWoS_S STAR¹iSTandard ARchitecture¹j¹v²π£ώ΄ü²Β²Ρ²Δ²ι¹BHBM2²…ëΈâû²Ζ²ι¹uSTAR 1.0¹v²Τ¹AHBM2E²…ëΈâû²Ζ²ι¹uSTAR 2.0¹v²π½pà”²Β²Ϋ¹B

SoC²ΤHBM²πç§çΎ²Ζ²ι¹uCoWoS_S¹v²Χç\꧲πïWèÄâΜ²Β²Ϋ¹uCoWoS_S STAR¹v²ΧäT½v¹mÉNÉäÉbÉN²≈ägëε¹n èoèä¹FTSMC¹iHot Chips 33²Χçuââ¹uTSMC packaging technologies for chiplets and 3D¹v²ΧÉXÉâÉCÉh²©²γ¹j

¹@ïWèÄâΜ²Β²Ρ²Δ²ι²Χ²ΆSiÉCÉ™É^¹[É|¹[ÉU²Χç≈ëεêΓ•@²ΤHBM²Χ¨¬êî¹A²Μ²ξ²©²γÉVÉäÉRÉ™É_ÉC²ΧɨÉCÉAÉEÉg²»²«²≈²†²ι¹Bç≈ëεç\ê§²Τ£Ü䑲Χç\꧹Aç≈è§ç\꧲Χ3²¬²Χäν•{éd½l²π¨Ύ΄q²ΆëI²Ή²ι¹B

¹@ç≈ëεç\꧲Ά¹AɨÉ`ÉNÉ΄²Χ2î{²…ë䙕²Ζ²ι‰I¨θ• ꜲΧSiÉCÉ™É^¹[É|¹[ÉU²πç≈ëεêΓ•@²Τ²Ζ²ι¹BSoC¹i²†²ι²Δ²ΆASIC¹j²π£Ü⦲…ɨÉCÉAÉEÉg²Β¹A²Μ²ΧçΕâE²…3¨¬²Η²¬²ΧHBM²πîz£u²Ζ²ι¹B£Ü䑲Χç\꧲ΆÉ¨É`ÉNÉ΄²Χ1.5î{²…ë䙕²Ζ²ι‰I¨θ• ꜲπSiÉCÉ™É^¹[É|¹[ÉU²Χç≈ëεêΓ•@²Τ²Ζ²ι¹BSoC²Ά£Ü⦲…ɨÉCÉAÉEÉg²Β¹A²Μ²ΧçΕâE²…2¨¬²Η²¬²ΧHBM²πîz£u²Ζ²ι¹Bç≈è§ç\꧲ΆÉ¨É`ÉNÉ΄²Χ1.3î{²…ë䙕²Ζ²ι‰I¨θ• ꜲπSiÉCÉ™É^¹[É|¹[ÉU²Χç≈ëεêΓ•@²Τ²Ζ²ι¹BSoC¹i²†²ι²Δ²ΆASIC¹j²ΧëΛ• ²…âà²Ν²Ρ2¨¬²ΧHBM²πîz£u²Β²Ρ²Δ²ι¹B

¹@ç≈ëεç\꧲©²γç≈è§ç\ê§²ή²≈²ΧïWèÄéd½l²Ά¹AHBM2ëΈâû²Χ¹uSTAR 1.0¹v²ΤHBM2EëΈâû²Χ¹uSTAR 2.0¹v²≈μ²γ²»²Δ¹B¹uSTAR 1.0¹v²ΧäJî≠éëéY²π¹uSTAR 2.0¹v²≈çΡ½‰½p²Ζ²ι²±²Τ²πà”é·²Β²Ρ²Δ²ι²φ²Λ²…¨©²Π²ι¹B

¹iéüâώ²…ë±²≠¹j

¹Υ¹uïü™cèΚ²ΧÉfÉoÉCÉX£ êM¹v‰AçΎÉoÉbÉNÉiÉ™Éo¹[àξ½½

Copyright © ITmedia, Inc. All Rights Reserved.

ä÷‰A΄Lé•

TSMC²Σ¨ξ²ι¹uN3¹vÉm¹[Éh²ΧèΎçΉ

TSMC²Σ¨ξ²ι¹uN3¹vÉm¹[Éh²ΧèΎçΉ

TSMC²Ά¨Μçί¹A¹uN5¹vÉvÉçÉZÉXÉm¹[Éh™K½pêΜïi²ΧêΕéY²πè΅£≤²…ägëε²Β²Ρ²Δ²ι²Τ²±²κ²Ψ²Σ¹A²Μ²ξ²π²≥²γ²…êiâΜ²≥²Ι²Ϋ¹uN4¹vÉm¹[Éh²Χ½ éY²π2021îN£Ü²…äJén²Ζ²ι½\£η²Ψ²Τî≠ï\²Β²Ϋ¹B²ή²Ϋ¹AN4²φ²η²ύ²≥²γ²»²ι΄Zèp™Iîρ•τ²πéά¨Μ²Ζ²ι²Τ²ί²γ²ξ²ι¹uN3¹vÉm¹[Éh²…²¬²Δ²Ρ²ύ¹A2022îN¨ψîΦ²…²Ά½ éY²πäJén²Ζ²ι¨vâφ²Ψ²Τ²Δ²Λ¹B ÉEÉGÉn¹[ÉXÉP¹[É΄²Χ£¥΄êëεÉvÉçÉZÉbÉT²πéά¨Μ²Β²Ϋ¹uInFO¹v΄Zèp

ÉEÉGÉn¹[ÉXÉP¹[É΄²Χ£¥΄êëεÉvÉçÉZÉbÉT²πéά¨Μ²Β²Ϋ¹uInFO¹v΄Zèp

¹uInFO¹v΄Zèp²πâϋ½«²Β²Ϋ2éμ½ό²ΧÉpÉbÉP¹[ÉW²Χ²Λ²Ω¹AÉEÉGÉn¹[΄K•Ά²Χ΄êëε²»ÉpÉbÉP¹[ÉWÉ™ÉO΄Zèp¹uInFO_SoW¹v²πâπêύ²Ζ²ι¹B ëΫëwîzêϋ²ΧÉrÉA£οçR²πëεïù²…£α¨Η²Ζ²ι¹uÉX¹[Ép¹[ÉrÉA¹v

ëΫëwîzêϋ²ΧÉrÉA£οçR²πëεïù²…£α¨Η²Ζ²ι¹uÉX¹[Ép¹[ÉrÉA¹v

çΓâώ²Ά¹Aäοêîî‘çܹi²†²ι²Δ²Ά΄τêîî‘çܹj²≈½ΉêΎ²Ζ²ιîzêϋëw¹i2ëwèψ²†²ι²Δ²Ά2ëwâΚ²Χîzêϋëw¹j²πêΎë±²Ζ²ιÉrÉA™d΄…²Χ£οçR²πëεïù²…âΚ²Α²ι΄Zèp¹A¹uÉX¹[Ép¹[ÉrÉA¹isupervia¹j¹v²…²¬²Δ²Ρâπêύ²Ζ²ι¹B ɲÉoÉCÉ΄¨ϋ²·è§¨^^ÉpÉbÉP¹[ÉW¹uInFO¹v²ΣêiâΜ

ɲÉoÉCÉ΄¨ϋ²·è§¨^^ÉpÉbÉP¹[ÉW¹uInFO¹v²ΣêiâΜ

TSMC²ΣäJî≠²Β²Ρ²Ϊ²ΫêφêiÉpÉbÉP¹[ÉWÉ™ÉO΄Zèp²Χç≈êV™°¨ϋ²πè–âν²Ζ²ι¹Bén²Ώ²ΆëSëΧ²ΧÉgɨəÉh²πéΠ²Ζ¹B ¹uÉVÉXÉeÉĹEêΜëΔ΄Π£≤ç≈™KâΜ¹iSTCO¹j¹v²Χéά¨Μ΄Zèp¹iëOj

¹uÉVÉXÉeÉĹEêΜëΔ΄Π£≤ç≈™KâΜ¹iSTCO¹j¹v²Χéά¨Μ΄Zèp¹iëOj

7nmà»ç~²Χ΄ZèpÉm¹[Éh²≈²Ά¹A¹uêί¨v¹EêΜëΔ΄Π£≤ç≈™KâΜ¹iDTCO¹j¹v²Ψ²·²≈²»²≠¹A¹uÉVÉXÉeÉĹEêΜëΔ΄Π£≤ç≈™KâΜ¹iSTCO¹FSystem Technology Co-Optimization¹j¹v²ύ½‰½p²Ζ²ι²±²Τ²≈PPA²†²ι²Δ²ΆPPAC²ΧÉoÉâÉ™ÉX²π£≤ê°²Ζ²ι²±²Τ²Σ΄¹²Ώ²γ²ξ²ι²φ²Λ²…²»²Ν²Ρ²Ϊ²Ϋ¹B ¹uÉVÉXÉeÉĹEêΜëΔ΄Π£≤ç≈™KâΜ¹iSTCO¹j¹v²Χéά¨Μ΄Zèp¹i¨ψj

¹uÉVÉXÉeÉĹEêΜëΔ΄Π£≤ç≈™KâΜ¹iSTCO¹j¹v²Χéά¨Μ΄Zèp¹i¨ψj

•{ÉVÉä¹[ÉY²Χç≈èIâώ²Τ²»²ιçΓâώ²Ά¹AëOâώ²…ë±²Ϊ¹uÉVÉXÉeÉĹEêΜëΔ΄Π£≤ç≈™KâΜ¹iSTCO¹j¹v²πâπêύ²Ζ²ι¹B