初のWoW技術適用で大幅性能向上、Graphcoreの新IPU:TSMCとの協業で実現(2/3 ページ)

Graphcoreが、第3世代のIPU(Intelligence Processing Unit)を発表した。業界初となる3D Wafer on Wafer(以下、WoW)技術適用のプロセッサだ。

2つの技術でプロセッサダイと、電源供給ダイを結合

GraphcoreはTSMCにとって、WoW技術関連の主要顧客である。

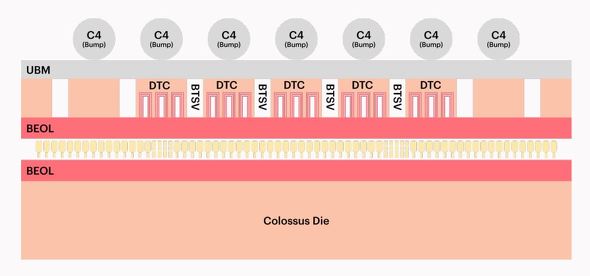

WoWチップには、プロセッサダイのウエハーと、電源供給ダイのウエハーの、2枚のウエハーが結合されている。電源供給ウエハーは、DRAMに情報を保存する場合と同様にディープトレンチキャパシターを備えており、それを電荷リザーバーとして使用し、プロセッサダイ上のトランジスタに超低インピーダンスで接続するという。

GraphcoreのCTO(最高技術責任者)を務めるSimon Knowles氏は、「このためトランジスタは、優れた電力効率で、より高速な動作が可能になる。プロセッサダイ向けのものと同じプロセッサ設計およびプロセス技術(TSMCの7nmプロセス)を使用しながら、Bow IPUプロセッサの正味の効果として、クロック速度の向上を実現することができるのだ」と述べる。

WoWは、2つの重要な技術に依存している。

ハイブリッド結合は、2枚のウエハーの金属面を合わせ格子状のバンプなしで結合することが可能だ。Knowles氏は、「これは、一種の冷間圧接のようなものだ。この方法のメリットとしては、ウエハー間のインターコネクトを超高密度化できるという点がある」と述べる。もう1つの重要技術は、新しいタイプのシリコン貫通ビア(TSV)「BTSV(Back-side TSV)」だ。

Knowles氏は、「WoWは、メモリダイをプロセッサダイの最上部に搭載するために使われているCoW(Chip on Wafer)技術とは異なる。この相違点が、WoWの接続ピッチのさらなる微細化を実現したのだ」と述べているが、ピッチに関する詳細は明かさなかった。

「ピッチの微細化の要因としては、2つの個別のダイではなく2つの完全なウエハーを容易に調整することができるという点と、電力供給ウエハーが極薄であるためにBTSV向けとしてイオンエッチングプロセスを適用できるという点が挙げられる。この薄型ウエハーはポリエチレンラップよりも薄く、透明で柔らかいため、薄型化する前に厚みのあるウエハーに結合させることにより、その後に続くプロセスステップの間、厚みのあるウエハーを機械的サポートとして機能させることができる。これは、個別のダイでは不可能なことだ」(Knowles氏)

さらに同氏は、「われわれは、TSMCとの間で約2年間にわたり、この技術分野における先駆的な顧客として協業してきた。この製造技術の実現には、膨大な作業量を要したため、もしわれわれのライバル企業が今から同様の取り組みを開始した場合、その実現にはかなりの長期間を要するだろう」と述べた。

Copyright © ITmedia, Inc. All Rights Reserved.