Avery、チップレットの検証IPを発表:UCIeの包括的サポートを提供

022年3月にチップレットの標準規格「Universal Chiplet Interconnect Express(UCIe)」が正式に策定された。これに伴い、米国のAvery Design Systemsは、チップレットの検証IP(intellectual property)を発表した。

2022年3月にチップレットの標準規格が正式に策定された。これに伴い、チップレットの検証IP(intellectual property)が米国のAvery Design Systems(以下、Avery)から発表された。

「PCI Express(PCIe)」や「Compute Express Link(CXL)」「HMB3」などの主要な半導体技術の機能検証ソリューションで知られるAveryは、チップレットの標準規格である「Universal Chiplet Interconnect Express(UCIe)」を適用するシステムのプレシリコン検証に対応した高品質のモデルとテストスイートでUCIeの包括的サポートを提供すると発表した。

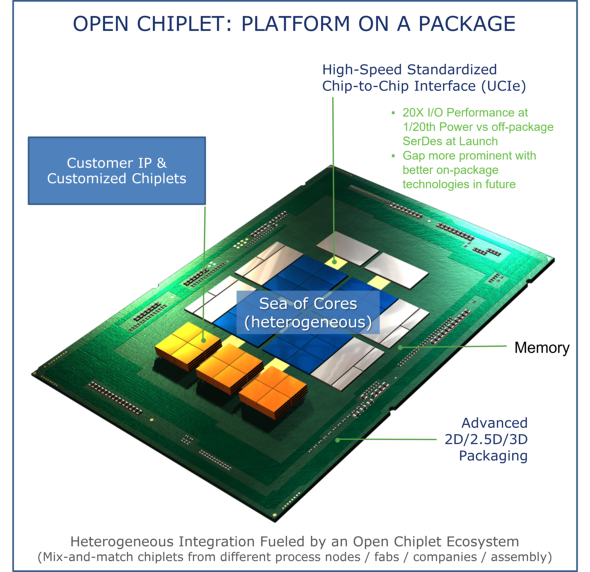

UCIeは2022年3月に発表されたチップレット間の通信標準規格で、Averyの他、同コンソーシアムの創設メンバーであるIntelやAMD、Arm、Qualcomm、TSMC、Samsung Electronics、ASE、Google、Microsoft、Metaなどによって策定された。同規格は、パッケージ内のチップレットの相互運用性をサポートし、チップレットのオープンエコシステムとパッケージレベルのユビキタスなインターコネクトを実現するものである。

UCIe規格の最初のイテレーションは、UCIeアダプターと(ダイ間のIO物理層、プロトコル、業界標準規格として確立されたPCIeおよびCXLを活用するソフトウェアスタックを含む)PHY、プロトコルに依存しないRAW転送モードに対応している。

Averyは、テスト済みの検証IP(VIP)ポートフォリオに基づく完全な機能検証プラットフォームを提供することで、設計要素のプレシリコン検証を可能にするという。同社のUCIe製品は、スタンドアロンのUCIeダイ間アダプターとLogPHYの検証の他、UCIeスタック上で動作する統合されたPCIeおよびCXL VIPもサポートする。UCIeモデルの他に、柔軟なオープンアーキテクチャを活用した包括的なプロトコルチェッカーやカバレッジ、リファレンステストベンチ、コンプライアンステストスイートも提供する。

チップレットは新しい技術ではない。大手半導体メーカーは、ムーアの法則による物理的限界に立ち向かうためにチップレットに注目してきた。チップレットを活用したシステムを設計する企業は、テストを実施して設計を検証する必要がある。だがAveryによれば、規格が正式に策定される前に、独自のダイ間接続インタフェースを使用していた顧客もいたという。

Averyのセールスおよびマーケティング担当バイスプレジデントを務めるChris Browy氏は、「ダイ間の接続に独自のIPを使用するクローズドシステムも悪くはない。しかし、標準規格があれば相互運用性や信頼性が向上する。同時に、異なるベンダーのダイ間の相互運用性に対する信頼性も高まるというメリットが得られる」と述べる。

「標準規格と検証IPの両方があれば、リスクが軽減され、チップベースの設計を手掛けるより多くの顧客に信頼性を提供できる」(同氏)

【翻訳:滝本麻貴、編集:EE Times Japan】

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

チップレットの普及拡大へ、「UCIe 1.0」が登場

チップレットの普及拡大へ、「UCIe 1.0」が登場

UCIe(Universal Chiplet Interconnect Express)は、パッケージ内のチップレットの相互接続を定義するオープン規格だ。UCIe策定の参加メンバー企業は、Advanced Semiconductor Engineering(ASE)、AMD、Arm、Google Cloud、Intel、Meta、Microsoft、Qualcomm、Samsung Electronics、TSMCの10社である。【訂正あり】 米新興企業、光I/OチップレットでNVIDIAと協業へ

米新興企業、光I/OチップレットでNVIDIAと協業へ

米国カリフォルニア州に拠点を置く新興企業Ayar Labsは、同社のチップ間光通信技術を中心としたエコシステムを構築するという。NVIDIAとの協業により、光I/O技術を適用した次世代アーキテクチャの開発に取り組んでいるところだ。 「ポストムーアの法則」の世界で高まる、試験の重要性

「ポストムーアの法則」の世界で高まる、試験の重要性

ポストムーアの法則に突入しても、半導体技術は引き続き、歩留まり向上の模索や新技術への方向転換など、進化を遂げていくだろう。例えば、複数の半導体ダイをヘテロジニアスに統合した高性能パッケージングや、チップレットなどが挙げられる。その結果、新しい製造プロセスの複雑性や欠陥が増すため、成功を実現するための要素として、試験の重要性が高まっていくとみられる。 「ムーアの法則」減速への打開策? ヘテロジニアス設計

「ムーアの法則」減速への打開策? ヘテロジニアス設計

半導体業界では現在、IoT(モノのインターネット)やビッグデータ、AI(人工知能)などによる新しい成長の波が押し寄せている。しかし、半導体イノベーションの必要性がこれまで以上に高まっているにもかかわらず、従来型のムーアの法則の2D(2次元)微細化は、減速の一途にある。 チップレットが主流になるための2つの要素

チップレットが主流になるための2つの要素

現在、データセンターのワークロードが急激な進化を遂げている。計算やメモリ、IOなどの機能が変化しながら組み合わさって、より高い計算密度が求められるようになってきた。このためアーキテクチャは、従来の「One-size-fits-all」型のモノリシックなソリューションから、ディスアグリゲーション(分離)された機能へと移行が進み、特定用途向けとして個別にスケーリングすることが可能になっている。 チップレットと3次元集積が「ムーアの法則」を牽引

チップレットと3次元集積が「ムーアの法則」を牽引

今回から、2021年8月にオンラインで開催された「Hot Chips」の技術講座より、「TSMC packaging technologies for chiplets and 3D(チップレットと3次元集積に向けたTSMCのパッケージング技術)」の講演内容を紹介する。