ƒiƒmƒVپ[ƒgژ_‰»•¨”¼“±‘ج‚ً—p‚¢‚½ƒgƒ‰ƒ“ƒWƒXƒ^ٹJ”پFŒ´ژq‘w‘حگد–@‚إ‹دˆê‚ةƒiƒm”––ŒŒ`گ¬

“Œ‹‘هٹw‚ئ“ق—اگو’[‰بٹw‹Zڈp‘هٹw‰@‘هٹw‚ج‹¤“¯Œ¤‹†ƒOƒ‹پ[ƒv‚حپA’ل‰·‚إŒ`گ¬‚إ‚«‚éƒiƒmƒVپ[ƒgژ_‰»•¨”¼“±‘ج‚ًƒ`ƒƒƒlƒ‹چق—؟‚ة—p‚¢‚ؤپAچ‚گ«”\‚©‚آچ‚گM—ٹ‚جƒgƒ‰ƒ“ƒWƒXƒ^‚ًٹJ”‚µ‚½پB

IGOƒiƒmƒVپ[ƒg‚ًƒQپ[ƒg‚إ•¢‚ء‚½Gate-All-Aroundچ\‘¢‚ً’ٌˆؤ

پ@“Œ‹‘هٹwگ¶ژY‹ZڈpŒ¤‹†ڈٹ‚جڈ¬—رگ³ژ،ڈy‹³ژِ‚ئپA“ق—اگو’[‰بٹw‹Zڈp‘هٹw‰@‘هٹw•¨ژ؟‘nگ¬‰بٹw—جˆو‚ج‰Y‰ھچsژ،‹³ژِ‚ç‚ة‚و‚鋤“¯Œ¤‹†ƒOƒ‹پ[ƒv‚ح2023”N6ŒژپA’ل‰·‚إŒ`گ¬‚إ‚«‚éƒiƒmƒVپ[ƒgژ_‰»•¨”¼“±‘ج‚ًƒ`ƒƒƒlƒ‹چق—؟‚ة—p‚¢‚ؤپAچ‚گ«”\‚©‚آچ‚گM—ٹ‚جƒgƒ‰ƒ“ƒWƒXƒ^‚ًٹJ”‚µ‚½‚ئ”•\‚µ‚½پB

پ@گو’[”¼“±‘ج‚حپA‚³‚ç‚ب‚éچ‚ڈWگد‰»‚âچ‚‹@”\‰»‚ھ‹پ‚ك‚ç‚ê‚ؤ‚¢‚éپB‚±‚¤‚µ‚½’†‚إپAژOژںŒ³چ\‘¢‚ب‚ا”¼“±‘ج‚جچ‚ڈWگد‰»‚ًگi‚ك‚ؤ‚¢‚‚¤‚¦‚إٹْ‘ز‚³‚ê‚ؤ‚¢‚é‚ج‚ھپuژ_‰»•¨”¼“±‘جپv‚إ‚ ‚éپBژ_‰»•¨”¼“±‘ج‚حپAٹù‚ةƒtƒ‰ƒbƒgƒpƒlƒ‹ƒfƒBƒXƒvƒŒƒC‚إ—p‚¢‚ç‚ê‚ؤ‚«‚½پB‚±‚جچق—؟‚ً”¼“±‘جڈWگد‰ٌکH‚ض‰—p‚·‚é‚ة‚حپA‹دˆê‚بƒiƒm”––Œ‚جگ»–Œ‹Zڈp‚ھڈd—v‚ة‚ب‚é‚ئ‚¢‚¤پB

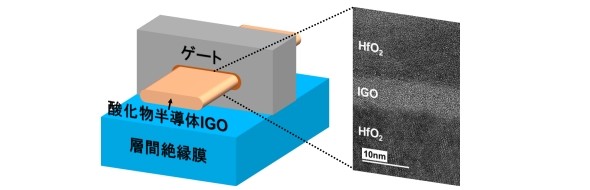

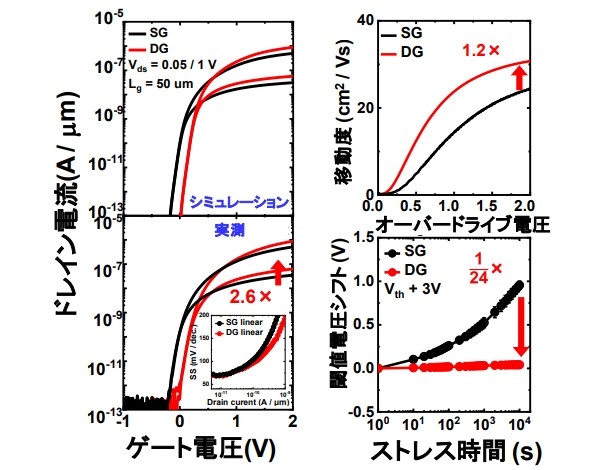

پ@Œ¤‹†ƒOƒ‹پ[ƒv‚حچ،‰ٌپAŒ´ژq‘w‘حگد–@‚ً—p‚¢ژ_‰»•¨”¼“±‘ج‚جƒiƒm”––Œ‚ًŒ`گ¬‚·‚é‹Zڈp‚ًٹJ”‚µ‚½پB‹ï‘ج“I‚ة‚حپAIn2O3‚ئGa2O3‚ًŒ´ژq‘w‚²‚ئپAŒًŒف‚ةگ¬–Œ‚ً‚µ‚ؤInGaOپiIGOپj‚جƒiƒm”––Œ‚ًŒ`گ¬‚µ‚½پB‚±‚جƒiƒmƒVپ[ƒgIGO‚ًƒ`ƒƒƒlƒ‹چق—؟‚ئ‚·‚éƒvƒŒپ[ƒiŒ^ƒgƒ‰ƒ“ƒWƒXƒ^‚ًژژچى‚µ‚½پB

پ@‚±‚جژژچى•i‚ً—p‚¢‚ؤپAˆع“®“x‚ئ‚µ‚«‚¢’lƒVƒtƒg‚ة‚¨‚¯‚éƒgƒŒپ[ƒhƒIƒt‚جٹضŒWگ«‚ة‚آ‚¢‚ؤ‰ً–¾‚µ‚½پB‚»‚جڈم‚إپAƒgƒŒپ[ƒhƒIƒt‚ج‰غ‘è‚ً‰ًŒˆ‚·‚邽‚كپAگV‚½‚ةIGOƒiƒmƒVپ[ƒg‚ًƒQپ[ƒg‚إ•¢‚ء‚½پuGate-All-Aroundچ\‘¢پv‚ًٹJ”‚µ‚½پBگV‚½‚بچ\‘¢‚ًچج—p‚µ‚½‚±‚ئ‚إپAپuƒmپ[ƒ}ƒٹپ[ƒIƒt“®چىپv‚âپuƒvƒŒپ[ƒiŒ^‚ة‘خ‚µ‚ؤ‹ى“®“d—¬‚ھ2.6”{Œüڈمپvپuˆع“®“x‚ح1.2”{Œüڈمپvپu‚µ‚«‚¢’l“dˆ³ƒVƒtƒg‚ج‘ه•‚ب’لŒ¸پv‚ًژہŒ»‚µ‚½‚ئ‚¢‚¤پB

Copyright © ITmedia, Inc. All Rights Reserved.

ٹضکA‹Lژ–

“Œ‹‘هپAژ_‰»•¨‘fژq‚إژ¥‹C’ïچR”ن‚ً10”{ˆبڈم‚ة

“Œ‹‘هپAژ_‰»•¨‘fژq‚إژ¥‹C’ïچR”ن‚ً10”{ˆبڈم‚ة

“Œ‹‘هٹw‚حپA’PŒ‹ڈ»ژ_‰»•¨‚ً—p‚¢‚ؤچىگ»‚µ‚½‹ژ¥گ«‘جپ^”¼“±‘جپ^‹ژ¥گ«‘جچ\‘¢‚ج‰،Œ^2’[ژq‘fژq‚إپAڈ]—ˆ‚ج10”{ˆبڈم‚ئ‚ب‚éژ¥‹C’ïچR”ن‚ھ“¾‚ç‚ꂽ‚ئ”•\‚µ‚½پB‚±‚جچ\‘¢‚ً—p‚¢‚ؤژژچى‚µ‚½3’[ژqƒXƒsƒ“ƒgƒ‰ƒ“ƒWƒXƒ^‘fژq‚إ‚حپAƒQپ[ƒg“dˆ³‚ة‚و‚ء‚ؤ“d—¬‚ً•د’²‚³‚¹‚邱‚ئ‚ة‚àگ¬Œ÷‚µ‚½پB RaaSپAگو’[”¼“±‘جگفŒvƒvƒ‰ƒbƒgƒtƒHپ[ƒ€‚ًٹJ”‚ض

RaaSپAگو’[”¼“±‘جگفŒvƒvƒ‰ƒbƒgƒtƒHپ[ƒ€‚ًٹJ”‚ض

“Œ‹‘هٹw‚âƒAƒhƒoƒ“ƒeƒXƒg‚ب‚ا‚ھ‘gچ‡ˆُ‚ئ‚µ‚ؤٹˆ“®‚·‚éپuگو’[ƒVƒXƒeƒ€‹ZڈpŒ¤‹†‘gچ‡پiRaaSپFƒ‰پ[ƒXپjپv‚حپA2023”N4Œژ1“ْ‚و‚èپuژںگ¢‘مگو’[”¼“±‘جگفŒvƒvƒ‰ƒbƒgƒtƒHپ[ƒ€پv‚جŒ¤‹†ٹJ”‚ًژn‚ك‚½پB ‘½گ”‚جƒxƒ“ƒ[ƒ“ٹآ‚©‚ç‚ب‚éپuƒ|ƒٹƒAƒZƒ“پv‚ًچ‡گ¬

‘½گ”‚جƒxƒ“ƒ[ƒ“ٹآ‚©‚ç‚ب‚éپuƒ|ƒٹƒAƒZƒ“پv‚ًچ‡گ¬

“Œ‹‘هٹw‚جŒ¤‹†ƒOƒ‹پ[ƒv‚حپA‘½گ”‚جƒxƒ“ƒ[ƒ“ٹآ‚ھ’¼گüڈَ‚ةکAŒ‹‚µ‚½پuƒ|ƒٹƒAƒZƒ“پv‚ًچ‡گ¬‚·‚邱‚ئ‚ةگ¬Œ÷‚µ‚½پB‘¾—z“d’r‚âƒiƒmƒfƒoƒCƒX‚ب‚ا‚ض‚ج‰—p‚ً–عژw‚·پB ƒOƒ‰ƒtƒ@ƒCƒgٹî”آڈم‚ة”¼“±‘جƒiƒm—تژqچ×گü‚ًچىگ»

ƒOƒ‰ƒtƒ@ƒCƒgٹî”آڈم‚ة”¼“±‘جƒiƒm—تژqچ×گü‚ًچىگ»

‹“s‘هٹw‚â“Œ‹‘هٹw‚ç‚جŒ¤‹†ƒOƒ‹پ[ƒv‚حپA–ٌ1nm‚ئ‚¢‚¤Œْ‚ف‚ئ•‚إپA’·‚³‚ھ1ƒتm‚ً’´‚¦‚锼“±‘ج‚جپuƒiƒm—تژqچ×گüپv‚ًچىگ»‚µ‚½‚ئ”•\‚µ‚½پB‚±‚ج—تژqچ×گüƒpƒ^پ[ƒ“‚حپAŒ´ژqƒXƒPپ[ƒ‹‚إƒ`ƒ…پ[ƒٹƒ“ƒO‹@چ\‚ھ‹N‚±‚èپAژ©”“I‚ةŒ`گ¬‚³‚ꂽ‰آ”\گ«‚ھچ‚‚¢‚ئ‚¢‚¤پB ”½‹ژ¥گ«‘ج‚إپuƒgƒ|ƒچƒWƒJƒ‹ƒzپ[ƒ‹Œّ‰تپv‚ًژہڈط

”½‹ژ¥گ«‘ج‚إپuƒgƒ|ƒچƒWƒJƒ‹ƒzپ[ƒ‹Œّ‰تپv‚ًژہڈط

“Œ‹‘هٹw‚حپAژ¥‰»‚ًژ‚½‚ب‚¢”½‹ژ¥گ«‘ج‚ة‚¨‚¢‚ؤپAپuƒgƒ|ƒچƒWƒJƒ‹ƒzپ[ƒ‹Œّ‰تپv‚ًژہڈط‚·‚邱‚ئ‚ةگ¬Œ÷‚µ‚½پBپuگV‚µ‚¢ژ¥‹Cڈî•ٌ”}‘ج‚ئ‚µ‚ؤٹˆ—p‚إ‚«‚é‰آ”\گ«‚ھ‚ ‚éپv‚ئ‚ف‚ؤ‚¢‚éپB “Œ‹‘ه‚çپAƒtƒBƒ‹ƒ€ڈَ—L‹@”¼“±‘جƒZƒ“ƒTپ[‚ًٹJ”

“Œ‹‘ه‚çپAƒtƒBƒ‹ƒ€ڈَ—L‹@”¼“±‘جƒZƒ“ƒTپ[‚ًٹJ”

“Œ‹‘هٹw‚ئƒtƒ@پ[ƒ€ƒVƒbƒv‚حپAƒJƒٹƒEƒ€ƒCƒIƒ“‚ًˆہ’è“I‚ةŒv‘ھ‚إ‚«‚éپuƒtƒBƒ‹ƒ€ڈَ‚ج—L‹@”¼“±‘جƒZƒ“ƒTپ[پv‚ًٹJ”‚µ‚½پB‚±‚جƒZƒ“ƒTپ[‚ً—p‚¢پAƒŒƒ^ƒX‚جچح”|ژہŒ±‚ةگ¬Œ÷‚µ‚½پB