Massive Computeデータセンターへの期待:光伝送技術を知る(21) 光伝送技術の新しい潮流と動向(2)(3/3 ページ)

光技術や光モジュール開発の動向をお伝えするシリーズ。今回は、データセンターの新しい動向を解説したい。

Back-End Network

今後の“Make Money”可能なAI/ML Systemをデータセンターに取り込むには、計算ノード、メモリ、ネットワークの3つのポイントがある(もちろん電力供給や冷却も乗り越えるべき障壁である)。スケーラビリティはもちろんフレキシビリティも求められるという。運用ではアプリケーションに最適なモデルに最適な計算ノードと最適なメモリを必要なだけ最適なネットワークで接続して無駄なく実行することが理想である。これはシステム設計の挑戦課題であるが、光部品業界もこれをサポートし大きなビジネスにしなければならない。

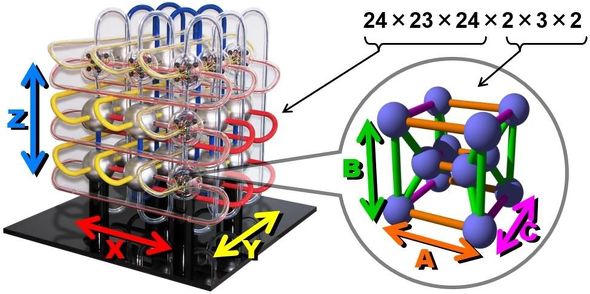

まず、最新のスーパーコンピュータやAI/MLはどのような構成になっているのだろうか。富岳では、2×3×2の12個のNode(チップ)を接続した“かたまり”をGroupとよび、それを24×23×24の3D Torusネットワークで接続した構成で15万8976個のチップを搭載するシステムを構築している(前出の[2]および図7)。

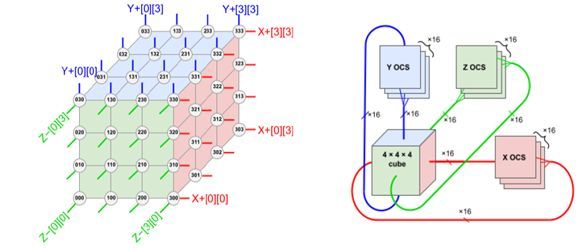

GoogleのAI、TPUv4は4×4×4(64チップ)の3次元メッシュのCube(立方体)を64個並べ、Cubeの1つの面から出る16(=4×4)ポートを16台の128×128の光回線スイッチ(Optical Circuit Switch: OCS)でCubeの対面へ配線接続するというシステム構成である[6](図8)。合計48台(16台×3面)の128×128のOCSが使用されている。ちなみに、TPUを64チップでCubeとした理由は1台のラックに収納できるからだからという。

[6]Norman P. Jouppi, Industry Track of ISCA 2023's program

数10K Nodeの次世代ではどのような構成になり、光技術はどう使用されるのだろうか。

以前から述べているDisaggregated Systemがキーワードであると考えている。計算ノードやメモリを効率よく柔軟に運用するには、それらをプール(Pool)し必要なリソースだけ構成(Composite)するDisaggregated Systemが有効だ。Compositeをどう実現するかがハード、ソフトの両面で大きな課題であり、その実現には膨大なデータを高速大容量、低レイテンシで転送する光技術が必須である。

図9は、NVIDIAが2020年の「GTC China」で発表したDisaggregated Systemの概念図である[7]。これによれば、GPUを2個搭載したモジュラー基板を横方向に8スロット並べ、それを9段に重ねた2×8×9=144個のGPU構成としている。それぞれのGPUの近傍にCPOが搭載されている。スイッチは、NVSwitchが1個搭載されたモジュラー基板が、8スロット×4段並んでいる。それぞれの基板に6個のCPOが搭載されている。このように小型集積化光モジュールを搭載したチップ数の少ないモジュラー基板を多数用いたSub-NodeとGPU間を接続するネットワークが予測される。消費電力が大きいので液浸冷却になるのかもしれない。

[7]NVIDIA GTC China 2020 Keynote

メモリからのデータの転送ネットワークは必要ないのだろうか。図10はMetaが示したFront-とBack-End Networkである[8]。太い白線がFront-End Networkで、細い白線がBack-End Networkだ。

Front-End NetworkはLeaf/Spineネットワークで、巨大ストレージにあるビッグデータをAI/MLに近いストレージあるいはSCM(Storage Class Memory)に送り込む。そして、xPUを効率的に動作させるためにxPUにデータをたゆまなく送り込む仕組み(Data Network)とバースト的に起こるxPUの計算出力を次のステージのxPUに送り込む仕組み(Compute Network)を使用して計算する。もちろん、Back-End Networkでは、同じOpticsを使用するのが合理的である。

[8]R. Stone, DCSK, OFC 2023

この新しいNetworkを実現するのに光インターコネクトが期待されている。その実用化には高速大容量、高集積・高並列、小型、低レイテンシ・低ビットエラー率、低消費電力、低コストといった課題を解決しなければならない。Ethernet Switchを想定した、従来議論されてきたCPO/NPOとは異なる、新しいIn-Box Optics(IBO)が生まれると考えている。

Disaggregated Systemを実現するプロトコルとしてCompute Express Link(CXL)が注目され、上記のBack-End Networkはそれに準拠したものになる可能性がある。ムーアの法則の集積度を維持するSiP(System in Package)、それに搭載するチップレットのUCIe(Universal Chiplet Interface Express)、そしてメモリインタフェースのOpen Memory Interface(OMI)などにより、CXLやDisaggregated Systemが可能になると考えている。次回以降はSiPやCXLを含む関連技術と標準、そして、Massive Computeデータセンターにおける光インターコネクト(Optical Interconnect)に関して述べたい。

筆者プロフィール

高井 厚志(たかい あつし)

30年以上にわたり、さまざまな光伝送デバイス・モジュールの研究開発などに携わる。光通信分野において、研究、設計、開発、製造、マーケティング、事業戦略に従事した他、事業部長やCTO(最高技術責任者)にも就任。多くの経験とスキルを積み重ねてきた。

日立製作所から米Opnext(オプネクスト)に異動。さらに、Opnextと米Oclaro(オクラロ)の買収合併により、Oclaroに移る。Opnext/Oclaro時代はシリコンバレーに駐在し、エキサイティングな毎日を楽しんだ。

さらに、その時々の日米欧中の先端企業と協働および共創で、新製品の開発や新市場の開拓を行ってきた。関連分野のさまざまな学会や標準化にも幅広く貢献。現在はコンサルタントとして活動中である。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

GFがシリコンフォトニクスプロセス「GF Fotonix」を発表

GFがシリコンフォトニクスプロセス「GF Fotonix」を発表

GlobalFoundries(GF)は2022年3月7日(米国時間)、次世代シリコンフォトニクスプラットフォームとして「GF Fotonix」を発表した。主にデータセンター向けソリューションを対象としたプロセスで、300GHz帯RF CMOSと光学コンポーネントを同一チップ上に集積する、300mmウエハー対応のモノリシックプラットフォームとなる。 クラウドに最適化したシリコンフォトニクスプラットフォーム

クラウドに最適化したシリコンフォトニクスプラットフォーム

Marvell Technology(以下、Marvell)は、クラウドに最適化した最新のシリコンフォトニクスプラットフォーム「400G DR4」の生産体制が整ったことを明らかにした。400G DR4は、増大する帯域幅の需要と人工知能や機械学習に依存した高度なアプリケーションに対応するように設計されている。 欧州が欧州半導体法「European Chips Act」の策定へ

欧州が欧州半導体法「European Chips Act」の策定へ

欧州委員会委員長であるUrsula von der Leyen氏が2021年9月15日(現地時間)、一般教書演説の中で、「European Chips Act(欧州半導体法)」の策定に関する発表を行った。中国政府が半導体イノベーションに数十億米ドル規模の資金を投じていることや、米国議会が半導体の戦略的価値について合意に達したことなどを受け、EUは、主体的な最先端技術の実現を目指す法案を策定し、競争に参入していく考えを表明した。 電磁波で電力を伝送するという夢の始まり(前編)

電磁波で電力を伝送するという夢の始まり(前編)

今回からはワイヤレス電力伝送の歴史を振り返る。 「光トランシーバー」は光伝送技術の凝縮

「光トランシーバー」は光伝送技術の凝縮

今回から、光トランシーバーについて解説する。データセンター、コンピュータや工場内ネットワークで使用される80km程度以下の中短距離光リンクを中心に、ストレージ、ワイヤレスやアクセス通信ネットワークなど、多様なアプリケーションで使用されている光トランシーバーを紹介する。 光ファイバーとシリコン光導波路を結合する技術

光ファイバーとシリコン光導波路を結合する技術

今回は、光ファイバーとシリコン光導波路を結合する技術を解説する。