1つのCPUを作って「完コピ」、Appleの理想的なスケーラブル戦略:この10年で起こったこと、次の10年で起こること(74)(2/3 ページ)

Appleのプロセッサ「M2」シリーズが出そろった。今回は、そのM2シリーズの解析結果から、Appleのチップ開発戦略をひもといてみよう。

シリコン総面積は2000mm2以上

図3は、M2 Maxをパッケージから取り外した様子である。シリコン上には、トランジスタとトランジスタ間を接続するための配線層があり、図3右は配線層込みの取り出した状態での様子である。

配線層があっても、おおよその内部の状態は分かる。チップ上部中央には、ハイパフォーマンスのCPUが8コアと、その左側に高効率CPUが4コアある。つまり、CPUはトータルで12コアだ。CPU下部には38コアのGPUがある。

GPUの左右は、LPDDR5のインタフェースだ。GPUの下部のインタフェース部は、M2 Max同士を接続するためのApple専用インタフェースとなっている(詳細は有償のテカナリエレポートに掲載)。M2 Maxを上下反転に配置し、インタフェース部でシリコンインターポーザーを介して接続すれば、M2 Ultraになる構造だ。M1 Maxを2個活用してM1 Ultraを作り出した実績のある方法である。

配線層のあるシリコンをくまなく観察すると、シリコン上に配線層で書き込まれたシリコン型名を探すことができる。M2 Maxのシリコン型名は「TMNM28」であった。多くの半導体には型名だけでなくメーカーロゴや年号情報などが乗っているが、Appleのシリコンは、シリコン型名だけのものが多い。

シリコン総面積は2000mm2を超える

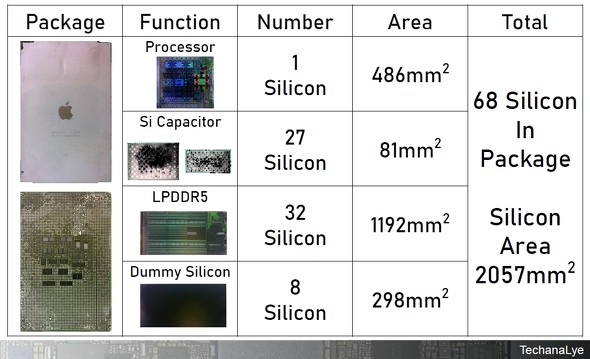

表1は、Apple M2 Maxのパッケージ内の全シリコンの使用個数、トータル面積などをまとめたものである。2010年以降スマートフォン向けやPC向けではプロセッサとハブコントローラー、プロセッサとメモリを1パッケージ化したSIP(System In Package)やPOP(Package On Package)、MCP(Multi Chip Package)、チップレットなど、多くの集約化技術が用いられている。

AppleはTSMCのInFO(Integrated Fan-Out)など技術を用い、1パッケージ内に機能チップと特性チップを組み合わせてプロセッサを作り上げている。プロセッサを取り囲むメモリ、プロセッサを支えるシリコンキャパシターという構造だ。M2 Maxだけでなくスマートフォン向けの「Aシリーズ」にも同じ構造を用いている。M2 MaxのパッケージAPL1111には、トータルで68個ものシリコンが入っている。機能系シリコンが33個、特性系が35個である。内部のトータルシリコン面積は、なんと2000mm2を超えている!

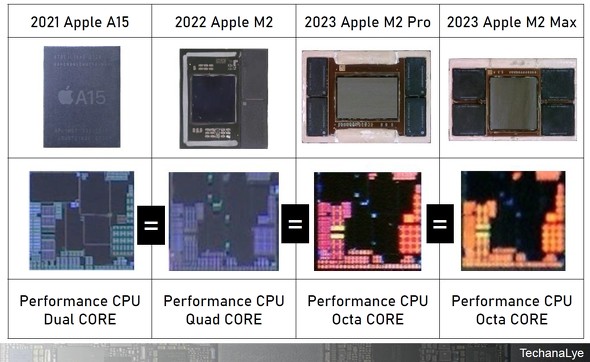

表2は、Apple製品のハイパフォーマンスCPUの1コアを拡大した写真である。若干解像度を落としているが、サイズ、形状などは4製品ともに同じものとなっている。

Copyright © ITmedia, Inc. All Rights Reserved.