裏面電源供給がブレークする予感、そしてDRAMも3次元化に加速 〜VLSI2023:湯之上隆のナノフォーカス(64)(7/7 ページ)

2023年6月に開催された「VLSIシンポジウム2023」は大盛況であった。本稿では、筆者が“ブレークの予感”を抱いた裏面電源供給技術と、3D(3次元) NAND/DRAM技術に焦点を当てて、解説する。

VLSI2023の総括

論文数および参加者数が異常に多いVLSI2023にリアル参加した。2019年以来、4年ぶりの対面での国際学会となったが、ほぼ1週間、集中して発表を聞くことができた。オンデマンドでは、なかなか集中的に視聴することができないので、1週間缶詰方式のVLSI2023は効率的だったと感じた。

発表内容としては、先端ロジック半導体について、世間の注目を集めているGAA方式のトランジスタより、裏面電源供給ネットワーク(BSPDN)が早期にブレークすることが予感された。

先端DRAMでは、Samsungが14nm(1a)世代に5層、EUVを適用することを発表し、今後、DRAMにもEUVの適用層数が広がっていくことが実感された。ただし、N+4世代(9nm?)付近で2次元の微細化が限界に達する可能性がある。そのため、メモリセルを縦方向にStackする3D DRAMが登場するかもしれない。

先端の3D NANDでは、ウエハーを−60℃以下の極低温による高アスペクト比(HAR)エッチングが実用化されていくと思われる。さらに、TELがHF/PF3という新しい絶縁膜エッチングのガス系を発見し、極低温(−60℃)と組み合わせることにより、より高精度で生産性の高い、3D NANDのメモリホール用のHARエッチングを開発した。このTELの技術によって、3D NANDの多層化はさらに進むだろう。

最後に、最先端露光装置EUVについて一言付け加えたい。計画では、ことし2023年後半から、ASML内のLabで、レンズの開口数が現行の0.33から0.55へ大きくなる、いわゆるHigh NAの開発が始まる。ところが、今回のVLSI2023でASMLは、レンズの開口数が0.75のHyper NAの構想があることを発表した(図14)。

図14[クリックで拡大] 出所:E. van Setten (ASML) “Advanced in EUV Lithography: From 0.33NA Technology towards High-NA and Beyond”, 2023 Symposium on VLSI Technology and Circuits, Short Course 1-2.

今回のVLSI2023で、ロジック半導体、DRAM、NANDのどの半導体も、新構造や新プロセスなどが開発されつつあることが分かった。これらの新技術と、EUV、High NA、そしてHyper NAが、相乗効果をもたらして行くと考えられる。半導体の進化は、今後もとどまることはないだろう。

訂正とお詫び

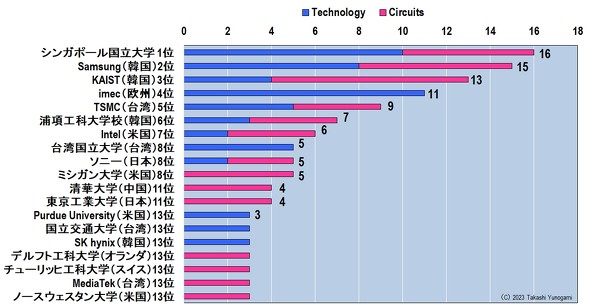

『投稿論文が激増した「VLSIシンポジウム2023」、シンガポール国立大が台頭』で、VLSI2023における、TechnologyとCircuitsを合計した機関別採択論文数のランキングのグラフを示した。ところがその後、Circuitsの機関別採択論文数に誤りがあることが明らかになった。TSMCがCircuitsに4件採択されているにも関わらず、それが反映されていなかった(尚、TSMC関係者からCircuitsは5件と聞いたが、1件は招待講演だったため、TSMCのCircuitsは4件とした)。

そこで、修正した「TechnologyとCircuitsを合計した機関別採択論文数のランキング」を図15に示す。第1位はシンガポール国立大学(16件)、2位はSamsung(15件)、3位は韓国KAIST(13件)、4位は欧州imec(11件)、5位はTSMC(9件)、6位は韓国の浦項工科大学校(7件)、7位が米Intel(6件)、8位が台湾国立大学、ソニー、米ミシガン大学(5件)となっている。

ここに修正したグラフを掲載するとともに、TSMC関係者にはお詫び申し上げます。

セミナー登壇のお知らせ

2023年8月21日(月)にサイエンス&テクノロジー主催で『ChatGPT(AI半導体)が巻き起こす半導体のビッグウエーブへの羅針盤』と題するセミナーを行います。

詳細はこちらをご参照ください。

筆者プロフィール

湯之上隆(ゆのがみ たかし)微細加工研究所 所長

1961年生まれ。静岡県出身。京都大学大学院(原子核工学専攻)を修了後、日立製作所入社。以降16年に渡り、中央研究所、半導体事業部、エルピーダメモリ(出向)、半導体先端テクノロジーズ(出向)にて半導体の微細加工技術開発に従事。2000年に京都大学より工学博士取得。現在、微細加工研究所の所長として、半導体・電機産業関係企業のコンサルタントおよびジャーナリストの仕事に従事。著書に『日本「半導体」敗戦』(光文社)、『「電機・半導体」大崩壊の教訓』(日本文芸社)、『日本型モノづくりの敗北 零戦・半導体・テレビ』(文春新書)。2023年4月には『半導体有事』(文春新書)を上梓。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

投稿論文が激増した「VLSIシンポジウム2023」、シンガポール国立大が台頭

投稿論文が激増した「VLSIシンポジウム2023」、シンガポール国立大が台頭

2023年6月に京都で開催される「VLSIシンポジウム2023」。ようやく、本格的なリアル開催が戻ってくるようだ。本稿では、デバイス分野のTechnologyおよび、回路分野のCircuitsそれぞれについて、投稿/採択論文数の分析を行う。 ここが変だよ 日本の半導体製造装置23品目輸出規制

ここが変だよ 日本の半導体製造装置23品目輸出規制

2023年3月、経済産業省は、半導体製造装置など23品目を輸出管理の対象として追加する方針を固めた。だが、ここで対象とされている製造装置、よくよく分析してみると、非常に「チグハグ」なのである。何がどうおかしいのか。本稿で解説したい。 半導体の微細化は2035年まで続く 〜先端ロジックのトランジスタと配線の行方

半導体の微細化は2035年まで続く 〜先端ロジックのトランジスタと配線の行方

2022年6月に開催された「VLSIシンポジウム」の講演のうち、最先端ロジック半導体に焦点を当てて解説する。ASMLが2023年から本格的に開発を始める次世代EUV(極端紫外線)露光装置「High NA」が実用化されれば、半導体の微細化は2035年まで続くと見られる。 なぜTSMCが米日欧に工場を建設するのか 〜米国の半導体政策とその影響

なぜTSMCが米日欧に工場を建設するのか 〜米国の半導体政策とその影響

本稿では、米国の半導体政策に焦点を当て、それが世界にどのような影響を及ぼしてきたか、または及ぼすと予測されるかについて論じる。 3Mが2025年末までにPFAS製造を停止、世界の半導体製造はどうなるのか

3Mが2025年末までにPFAS製造を停止、世界の半導体製造はどうなるのか

3M社が2025年末までにPFAS製造から撤退するという。世界の半導体製造は一体どうなってしまうのだろうか。 リーマン・ショック級のメモリ不況の到来 〜その陰にIntelの不調アリ

リーマン・ショック級のメモリ不況の到来 〜その陰にIntelの不調アリ

半導体市場の不調が明らかになっている。本稿では、世界半導体市場統計(WSTS)のデータ分析を基に、今回の不況がリーマン・ショック級(もしくはそれを超えるレベル)であることと、その要因の一つとしてIntelの不調が挙げられることを論じる。