パッケージのサイズからは判別不能 「シリコン面積比率」が示す高密度実装:この10年で起こったこと、次の10年で起こること(79)(1/3 ページ)

近年、半導体ではパッケージの高密度化が進んでいる。パッケージのサイズからは、搭載されているシリコンの“総面積”は分からない。今回は、2023年に登場した話題のプロセッサを、「パッケージ面積に対するシリコン面積の比率」という観点で見てみよう。

高密度化が進む半導体パッケージ

半導体の高集積化は微細化と高密度パッケージングの両輪で進んできた。ここ数年はHBM(広帯域メモリ)、チップレット、多層積層メモリなどが大きな話題になっている。1つのパッケージ内に複数のチップを入れる技術は古くから使われている技術で、MCM(Multi CHIP Memory:DRAMとNANDフラッシュメモリとコントローラーを1パッケージに搭載したもの)、MCP(Multi CHIP Package:プロセッサとI/Oコントローラーを1パッケージに並べて配置したもの)、SIP(Silicon In Package:コントローラーとDRAMやNORフラッシュメモリなどを1パッケージ内に重ねたもの)が多くの製品に活用されている。通信用のパワーアンプは3G(第3世代移動通信)時代からモジュール化されており、MCM(Multi CHIP Module :アンプやフィルターなど10チップほどが入っている)がほとんどになっている。

電子機器で10パッケージに見えるシステムも中身を開封すると複数のチップが入っており、実際のシリコン数では2倍以上になることも多い。あまりに作業量が大きいので弊社では一度しか行ったことがないが、「iPhone」に搭載される全パッケージを開封したことがある。テカナリエレポートの49号に詳細が掲載されている。例えば、全37パッケージで構成される「iPhone 7」のパッケージ内部の総シリコン数は113個(ただしMEMSマイクロフォン除く)。つまり、実際のシリコン数は、パッケージ数の実に3.05倍になっている。

現在、多くのシステムはパッケージ外観で中身を判断できなくなっている。1つのパッケージ内に多くの機能が収まっているからだ。多くの電子機器は、工具さえあれば誰でも分解できるので、パッケージ外観を見ることはできる。しかし、現在の高度な電子機器は1つのパッケージに複数のシリコンが入っているものが増えている。外だけ見ても仕方ない。今回は内部に入っているシリコンの総面積とパッケージ面積の比率という観点から、2023年に話題となった数チップを報告したい。

「iPhone 15 Pro」のプロセッサ「A17 Pro」

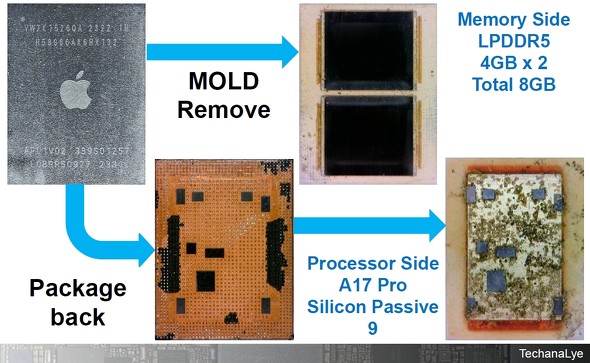

図1は、2023年9月に発売されたApple「iPhone 15 Pro」に搭載されている、3nm世代で製造された「A17 Pro」のパッケージ内の様子である。

Appleロゴマーク側にDRAMが実装され、反対側にはA17プロセッサと電源安定化のためのシリコンキャパシターが埋め込まれている。メモリは2社のサプライヤーを利用していて、Micron Technology製とSK hynix製がある(若干構成が異なる)。ともにLPDDR5メモリと補強用のダミーシリコンが積層されており、メモリ側は6シリコンとなっている。

プロセッサ側にはプロセッサ1シリコンに対してメモリインタフェース(大電流を多ビット動作)、CPU、GPU、NE(Neural Engine)などの高速動作の演算器の直上にシリコンキャパシターが配置されている。シリコンキャパシターはトータルで9シリコンとなっている。A17 Proのパッケージ内には16シリコンが入っているわけだ。

機能シリコンだけでなくキャパシターといった特性に寄与するシリコンも埋め込まれており、機能特性実現パッケージとなっている。弊社では取り出した全シリコンのサイズ(製造プロセスの判定含め)測長を行い、シリコン面積を求めている。シリコン面積が明確になるとウエハー1枚からの取得数も求められるので、詳細(欠陥の考え方など)は省略するがおおよその1シリコン当たりのコスト算出(誤差はある)もメドが立つ。価格を決めるのは歩留まり、総出荷数など多くの要素があるが、シリコン面積が分かればコスト算出の精度は高くなる。

Copyright © ITmedia, Inc. All Rights Reserved.