「電流を流すだけで積和演算」 TDKの超省電力AI用デバイス:消費電力はGPU比で100分の1(2/2 ページ)

TDKは、スピントロニクス技術を活用するニューロモーフィック素子として「スピンメモリスタ」を開発した。AIで多用される積和演算を、GPUに比べて100分の1の消費電力で実行できるという。フランスCEAと東北大学との協業により、2030年の量産技術の確立を目指す。TDKは、スピンメモリスタのデモを「CEATEC 2024」で公開する予定だ。

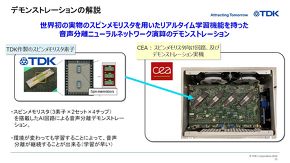

スピンメモリスタの実素子を用いたデモをCEATECで披露

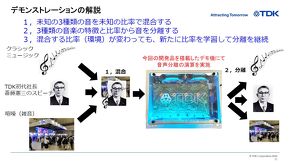

TDKは2020年からフランスの研究機関CEAと協業し、スピンメモリスタを用いたAIデバイスの開発を進めている。この協業によりTDKは、スピンメモリスタを搭載したAI回路で音声分離を行うコンセプトデモを完成させ、CEATEC 2024で披露する。

デモでは、クラシック音楽とスピーチ、雑音の3種類の音を未知の比率で混合する。AI回路は3種類の音をリアルタイムで学習しながら聞き分け、分離していく。雑音が大きくなるなど混合する比率が変わっても、リアルタイムで学習し直して分離を継続する。一般的なAI(機械学習)で同様の音声分離を行う場合、音を事前に学習する必要があるため、混合する比率が変わるとそれに対応することは難しい。

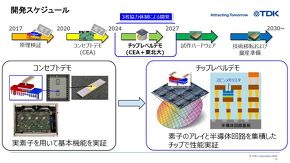

2030年にも量産技術の確立へ

TDKは今後、スピントロニクス研究に強い東北大学も加えた3者連携により、12インチウエハーでスピンメモリスタアレイと回路を試作し、チップレベルでの性能検証を進める。2027年までの実用化と、2030年までの量産技術確立を目指す。「集積する際の課題として歩留まりが挙げられる。歩留まりを向上させつつ、いかに集積を拡大していくかが鍵になる」(TDK)

スピンメモリスタ自体の性能改善も進める。TDKは「材料レベルからの開発が欠かせない。具体的には、スピンメモリスタの磁壁をゆっくりと安定して動かせるような材料が必要になる」と語った。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

TDKが車載用コンデンサーを開発 MLCCを横に3つ並べて大容量化

TDKが車載用コンデンサーを開発 MLCCを横に3つ並べて大容量化

TDKは2024年9月10日、積層セラミックコンデンサー(MLCC)2〜3個を金属端子で接合した金属端子付き多連型メガキャップ「CA」シリーズで、車載向けの新製品を開発したと発表した。従来は縦に重ねていたMLCCを横に並べる新構造を採用。「業界最大」(同社)という3連化を実現し、静電容量を従来比最大1.5倍にした。 エネルギー密度100倍の全固体電池向け新材料、TDK

エネルギー密度100倍の全固体電池向け新材料、TDK

TDKは、充放電可能なセラミック全固体電池「CeraCharge」の次世代品に向けて、従来の約100倍のエネルギー密度の全固体電池用材料を開発したと発表した。 病院の待合室で心臓検査が可能に? TDKの高感度磁気センサー

病院の待合室で心臓検査が可能に? TDKの高感度磁気センサー

TDKと東京医科歯科大学は、磁気シールドのない通常環境で、MR磁気センサーを使った心臓活動の計測に成功した。今後、病院の待合室などでより手軽に心臓検査を行えるようになると期待する。さらに、心電図では難しい疾患の診断、胎児の心臓の評価などが可能になる見込みだ。 TDK、AIの新会社をシンガポールに設立

TDK、AIの新会社をシンガポールに設立

TDKは、AI(人工知能)関連の新会社としてシンガポールに「TDK SensEI」を2024年7月8日付けで設立した。新会社では、AI技術と複数のセンサーをエッジ側で融合させたプラットフォームの開発などを行う。 アルミホイルより薄い! 厚さ6μmの低周波ノイズ対策用パーマロイシート

アルミホイルより薄い! 厚さ6μmの低周波ノイズ対策用パーマロイシート

TDKは2024年5月16日、低周波ノイズ対策用の超薄型パーマロイシート「IPM series」の販売を開始した。高透磁率材「パーマロイ合金」を使用したもので、自動車の電動化に伴って増加する低周波ノイズの遮蔽に貢献する。