板厚7.6mmで124層、HBMウエハー検査装置用PCBを開発:極薄材料や工具の独自開発で実現

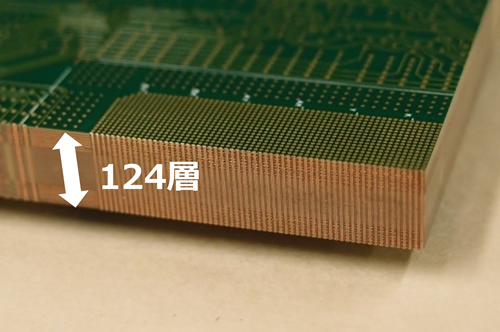

OKIサーキットテクノロジーは、広帯域メモリ(HBM)向けウエハー検査用に124層プリント配線板(PCB)を開発した。板厚を7.6mmに抑えたままで、従来比15%の多層化に成功した。

OKIグループのプリント配線板(PCB)事業を手掛けるOKIサーキットテクノロジー(以下、OTC)は2025年4月24日、広帯域メモリ(HBM)向けウエハー検査装置用に、124層PCBを開発したと発表した。従来の108層から約15%多層化した。半導体検査装置用に多層/高精細/大型のPCBを開発、生産する上越事業所(新潟県上越市)において、同年10月までに量産技術の確立を目指す。

AI演算においてGPUとともに需要が急増しているHBMは、ウエハーを高精度で薄く加工する。そのため、検査装置用PCBにも、より高い性能と品質が求められるようになっている。

さらに、最新の半導体では、信号数が多く、プロセスの微細化でウエハー搭載チップ数も増加するので、検査装置用PCBは高密度化と積層数の増加が必要になる。一方、各種の制約により板厚を7.6mmに抑える必要があり、これまでは108層が限界だった。今回OTCは、極薄材料の開発や、極薄材料に対応した治工具、ハンドリング技術を開発した他、同社独自の極薄材料自動搬送装置を開発し、ラインに導入することで、板厚を7.6mmに抑えつつ124層の多層化に成功した。

OKIはリリースで、EMS事業に積極的に取り組んでいて、特にPCB事業での技術開発を重視しているとコメント。AI半導体や航空宇宙、防衛、ロボット、次世代通信など、今後の成長が期待される分野に対応すべく今回の124層PCB技術を開発したと述べた。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

超高速DRAM技術「HBM」の基礎

超高速DRAM技術「HBM」の基礎

今回は、「3次元(3D)技術はDRAM開発にとって援軍ではあるが救世主ではない」という事実とともに、3D技術を用いた超高速DRAM「HBM」とはどのようなDRAMなのかを紹介していく。 DDR4とHBMの長所と短所

DDR4とHBMの長所と短所

今回は、HBM(High Bandwidth Memory)とDDR4 DRAMを、データ転送速度やパッケージングなどの点から比較してみる。後半は、埋め込みDRAM(eDRAM)の説明に入る。ARM ReserchのRob Aitken氏は、eDRAMが「ニッチな市場にとどまる」と予想しているが、それはなぜだろうか。 超高速DRAM技術「HBM」の基礎

超高速DRAM技術「HBM」の基礎

今回は、「3次元(3D)技術はDRAM開発にとって援軍ではあるが救世主ではない」という事実とともに、3D技術を用いた超高速DRAM「HBM」とはどのようなDRAMなのかを紹介していく。 AIブームで脚光を浴びるHBM 販売台数は2035年に15倍に

AIブームで脚光を浴びるHBM 販売台数は2035年に15倍に

AIデータセンターの需要が成長する中、ワークロード並列処理をサポートする広帯域幅メモリ(HBM)の注目度が高まっている。HBMの販売台数は、2035年までに2024年の15倍に成長すると見込まれている。 過熱するHBM開発競争、SK hynixは製品化を前倒し

過熱するHBM開発競争、SK hynixは製品化を前倒し

SK hynixは、次世代HBMである「HBM4」製品について、従来の想定より1年早い2025年に発表予定だと明かした。同社はHBM市場で大きなシェアを確保しているが、専門家は「今後、より厳しい競争に直面することになるだろう」と語っている。