「業界初」2nm SRAMがAIデータセンターで果たす役割:Marvell Technologyが開発

SRAMは、さまざまな場所で必要とされるがイノベーションが起こらない、「配管」のような存在だと見なされている。Marvell Technologyは「業界初」(同社)だという2nmのカスタムSRAMを開発し、SRAMのイノベーションを目指している。

SRAMは、今や市販の「配管」のような存在として認識されるほど定着したメモリとなったが、Marvell Technology(以下、Marvell)の最新のカスタムSRAMは、この既存メモリがAIデータセンターにおいてどのような役割を担うのか実証しようとしている。

消費電力とダイ面積を大幅に削減

Marvellは同社のカスタムSRAMを「業界初となる2nmのカスタムSRAM」だとしている。アクセラレーテッドインフラストラクチャ内のメモリ階層の性能を高め、最大6Gビットの高速メモリを提供することで、カスタムXPU(プロセッサ、アクセラレーター、GPU)/デバイスの性能向上を実現する設計だ。また、同じ密度でメモリ消費電力とダイ面積を大幅に削減できるという。

同社のSRAMは、密度が同程度の標準的なオンチップSRAMと比べて消費電力を最大66%削減していて、最大3.75GHzで動作する。消費電力は、エネルギーフットプリントを管理して効率的に部品を冷却したいAIクラスタやデータセンターにとって重要な指標だ。

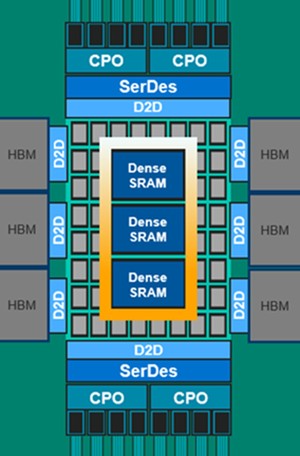

MarvellのリードメモリアーキテクトであるDarren Anand氏は、米国EE Timesとのブリーフィングの中で「Marvellは、AI/機械学習アプリケーション向けたSRAMの最適化に力を入れてきた。われわれが現在取り組んでいるパッケージングやカスタム広帯域メモリ(HBM)の取り組みとの相乗効果が非常に大きく、XPU上でより多くのダイ面積をコンピューティングに解放できる」と述べている。

「SRAMにはイノベーションのチャンスがある」

Anand氏は「MarvellのSRAMは常にHBMにアクセスするのではなく、一部のワークロードをダイ上で保持し、AIワークロードに必要な高帯域幅や幅広いIOをサポートする。これによって、デバイス全体のパフォーマンスを高められる可能性がある」と述べる。

「SRAMは、1桁台のプロセスノードで利用できる唯一のメモリなので、ニアメモリコンピューティングアーキテクチャをサポート可能な唯一の高性能メモリだ。このような最先端ノードでは、同じシリコン上にDRAMを搭載することはできない。同様に、NANDフラッシュメモリや磁気抵抗メモリ(MRAM)、抵抗変化型メモリ(ReRAM)、相変化メモリ(PCM)などの新興メモリも、最先端ノードでは利用できない」(同氏)

Anand氏は「SRAMは最先端ノードのロジックと同じダイに組み込んで、XPU上のプロセッサやロジックエンジンなどが即座に利用できるメモリ階層をサポートできる」と説明する。この点で、メモリとロジックを接続する一般的なノイマン型アーキテクチャとは異なっている。ニアメモリコンピューティングアーキテクチャは、必要とされる場所のより近くにデータを配置することで、データ移動に必要な電力を低減しながら帯域幅を拡大できる。

同氏は「典型的なXPUでは、シリコン面積の少なくとも30%がSRAM専用とされ、中にはダイ面積の50〜60%を超える設計もある。われわれがそれを最適化しようとしているのは、チップのダイサイズやコストを大きく変えられるからだ」と付け加えた。

「業界では、SRAMは基本的なIP(Intellectual Property)の『配管』のような存在になりつつある。つまり、さまざまな場所で必要とされるが、技術的なイノベーションが全くないということだ。実際には、SRAMアーキテクチャに実装できる新しい技術は多く存在し、電力や帯域幅をはじめ、その他のさまざまなメトリクスを最適化できる。私たちはSRAMを単なる配管としては見ない。むしろイノベーションのチャンスだと考えている」(Anand氏)

Anand氏によると、SRAMの最大の課題は面積のスケーリングだという。これまでロジックとメモリはいずれも、何世代にもわたってスケーリングされてきたが、SRAMセルは壁にぶつかり始めたとみられ、過去数世代の先進ノードのスケーリングが伸び悩んでいる。Anand氏は「ロジックは引き続きスケーリングしているが、メモリビットセルはそうではない」と指摘する。

Objective Analysisの主席アナリストであるJim Handy氏は「Marvellの手法は、SRAMチップがプロセスに比例して微細化していないという事実を受け入れながら、電力削減と速度向上を実現している。同社はこのようなプロセスジオメトリに対し、SRAMをわずかながら微細化させているのだ」と述べている。

Handy氏は「SRAMは、高性能プロセッサチップ上のキャッシュメモリに広く使われている。チップがメモリを使用するために外部メモリにアクセスする必要がなければ、さらに高速化できる。実際、チップに搭載されている全てのコアがサイクルごとに1つの命令を実行でき、非常に高速だ」とした。

【翻訳:田中留美、編集:EE Times Japan】

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

「N2」SRAMの歩留まりは90%以上 技術開発も好調のTSMC

「N2」SRAMの歩留まりは90%以上 技術開発も好調のTSMC

TSMCは同社顧客向けの技術発表会「TSMC 2025 Japan Technology Symposium」を開催。TSMC ジャパン 社長の小野寺誠氏、TSMC Senior Vice President 兼 Deputy Co-COO(副共同最高業務執行責任者)のKevin Zhang氏が同社の先端プロセスに関する取り組み状況などについて語った。 AIシステムの「メモリの障壁」を取り除く MRAMで挑む米新興

AIシステムの「メモリの障壁」を取り除く MRAMで挑む米新興

米スタートアップのNumemは、MRAMベースの同社のメモリ「NuRAM」によって、AIシステムにおけるメモリのボトルネックを解消しようと取り組んでいる。 「標準化を待てず」 HBMで変わるメモリ技術サイクル

「標準化を待てず」 HBMで変わるメモリ技術サイクル

広帯域メモリ(HBM)の技術進化が加速している。GPUの進化に合わせるために、カスタマイズや独自アーキテクチャの採用が求められるようになっていることもあり、標準化の完了を「待っていられない」状態になりつつある。 Samsungの半導体四半期業績、前期比で増収も利益率は1.4%に激減

Samsungの半導体四半期業績、前期比で増収も利益率は1.4%に激減

本稿では、Samsung Electronicsの2025年度第2四半期(2025年4月〜6月期)の四半期業績を紹介する。半導体部門の営業利益が大きく低下した。 キオクシアの四半期業績、前期比では減収増益に

キオクシアの四半期業績、前期比では減収増益に

本稿では、キオクシアホールディングスの2025会計年度(2026年3月期)第1四半期(2025年4月〜6月期)を紹介する。