キヤノンと日本シノプシスがRapidusに委託へ:2nm GAAプロセス活用

キヤノンと日本シノプシスは2026年3月3日、新エネルギー・産業技術総合開発機構(NEDO)の公募事業に採択された次世代半導体の設計技術開発プロジェクトに参画すると発表した。両社はRapidusの2nm GAA(Gate All Around)プロセスを活用する。

キヤノンと日本シノプシスは2026年3月3日、新エネルギー・産業技術総合開発機構(NEDO)の公募事業に採択された次世代半導体の設計技術開発プロジェクトに参画すると発表した。両社はRapidusの2nm GAA(Gate All Around)プロセスを活用しチップを試作する。

2nmとチップレット技術を活用

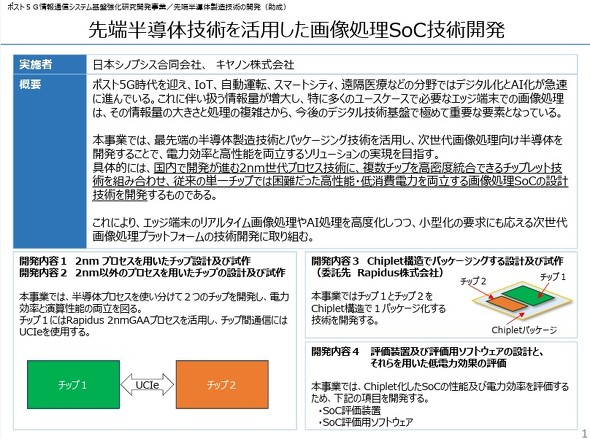

キヤノンと日本シノプシスはNEDOが公募した「ポスト5G情報通信システ厶基盤強化研究開発事業/先端半導体製造技術の開発(助成)」に採択された研究開発プロジェクト「先端半導体技術を活用した画像処理SoC技術開発」に参画すると発表した。同プロジェクトでは、キヤノンの画像処理技術、日本シノプシスの設計技術を融合し、NEDOの支援のもと、次世代画像処理向け半導体の設計技術開発に共同で取り組む。

両社は、2nm世代の微細プロセス技術を基盤に、複数チップを高密度に統合するチップレット技術を組み合わせることで、従来の単一チップ構成では実現が困難だった高性能かつ低消費電力な画像処理SoC(System on Chip)の設計技術を開発すると説明。これによって、「エッジ端末におけるリアルタイム画像処理やAI処理の高度化に対応しつつ、省電力化や小型化にも貢献することを目指す」としている。

具体的にはまず、半導体プロセスを使い分けて2つのチップを開発し、電力効率と演算性能の両立を図る。そのうちチップ1にRapidusの2nm GAAプロセスを活用し、チップ間通信にはUCIeを使用。さらにチップ1とチップ2をチップレット構造でパッケージングする設計および試作をRapidusに委託する(下図)

キヤノンは「長年培ってきた画像処理技術とものづくりの強みを生かし、日本の先端半導体技術開発の加速と産業基盤の強化に貢献する。本プロジェクトを通じて、次世代半導体の研究開発を支え、イメージングやAI分野で技術の発展に寄与する」と述べている。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

Rapidus、総額2676億円を調達 「日本経済に20兆円貢献」期待

Rapidus、総額2676億円を調達 「日本経済に20兆円貢献」期待

Rapidusは2026年2月27日、政府と民間から総額約2676億円の資金調達を実施したと発表した。政府からは約1000億円、民間からはNTTやキヤノン、ソニーグループ、ソフトバンクなど32社が合計約1676億円を出資し、資本金・純資本金の総額は約2749億5000万円になる。 TSMCは2nmで主導権維持、SamsungとIntelに勝機はあるか

TSMCは2nmで主導権維持、SamsungとIntelに勝機はあるか

米国EE Timesが調査した複数のアナリストによると、TSMCは、最近生産開始を発表した2nmプロセスによって、今後数年にわたって高度な半導体ノードでライバルのSamsungとIntelを凌ぐ見込みだという。 2026年の半導体市場を占う10の注目トピック

2026年の半導体市場を占う10の注目トピック

ことし2026年の半導体市場を占う意味で、筆者が注目すべきトピックを独断と偏見で10件ほどピックアップしてみた。 Rapidus、千歳で製造した2nm GAAトランジスタの試作品を初展示

Rapidus、千歳で製造した2nm GAAトランジスタの試作品を初展示

Rapidusは「SEMICON Japan 2025」(2025年12月17〜19日)に出展し、北海道千歳市の開発/製造拠点「IIM(イーム)」で製造した2nm GAA(Gate All Around)トランジスタや600mm角 再配線層(RDL)インターポーザーパネルの試作品を展示した。 Rapidus、600mm角インターポーザーパネルを初披露 NVIDIAの受託にも意欲

Rapidus、600mm角インターポーザーパネルを初披露 NVIDIAの受託にも意欲

Rapidus 社長兼CEOの小池淳義氏は「SEMICON Japan 2025」内のセミナープログラムに登壇。同社が掲げるビジネスモデル「RUMS(Rapid and Unified Manufacturing Service)」や前工程/後工程の最新の取り組みを紹介したほか、600mm角の再配線層(RDL)インターポーザーパネルの試作品を披露した。 AIで半導体設計時間を半減 Rapidusの2nm向け支援ツール

AIで半導体設計時間を半減 Rapidusの2nm向け支援ツール

Rapidusは2025年12月17日、同社2nm製造プロセス向けの半導体設計支援ツール群「Raads」を発表した。2026年から順次リリース予定で、設計期間の50%短縮と、設計コストの30%削減が可能だとしている。