AI/HPCシステムの死命を制する消費電力・放熱設計(後編):福田昭のデバイス通信(512) TSMCが解説する最新のパッケージング技術(9)(1/2 ページ)

「IEDM 2025」におけるTSMCの講演内容を紹介するシリーズ。前編に続き、「(3)Thermal dissipation design(消費電力および放熱の設計)」の内容を解説する。

(ご注意)今回は前編の続きです。まず前編を読まれることを強く推奨します。

熱伝導材料(TIM)と冷却方式の改良でTDPを高める

前編(前回)では、STCO(システムと製造の協調最適化)で考慮すべき5つの事柄の3番目である「(3)Thermal dissipation design(消費電力および放熱の設計)」の概要説明を始めた。AI/HPCプロセッサの最大消費電力(TDP)が最近になって急激に増加していること、プロセッサやメモリなどを収容する先進パッケージ各部の熱抵抗がTDPを制限すること、などを述べた。

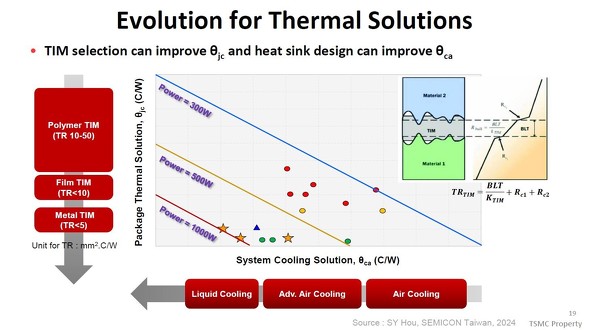

熱抵抗を大きく左右するのは、熱伝導材料(TIM:Thermal Interface Material)と冷却手法(放熱手法)である。TIMの熱抵抗(平方ミリ・℃/W)は材料によって大幅に異なる。ポリマーだとTIMの熱抵抗は10〜50とかなり大きい。薄膜化すると10以下、金属だと5以下と大幅に低くなる。ただしTIMの接続相手は表面が平坦ではなく、接続界面での熱抵抗が重要である。

冷却方法では、従来式の強制空冷が一般的であり、コストが低い。ただし熱抵抗はあまり低くない。熱抵抗を下げた改良版の強制空冷、さらには液体冷却がハイエンドのシステムで採用されつつある。

パッケージの熱抵抗(縦軸、シリコンダイのpn接合からパッケージのケースまで)とシステムの熱抵抗(横軸、パッケージのケースから周囲環境まで)[クリックで拡大] 出所:TSMC(IEDM 2025のショートコース(番号SC1-5)で公表された講演スライドから)

パッケージの寸法拡大でパッケージの反り量が増加

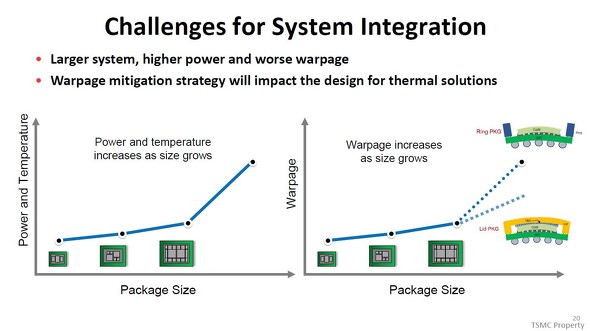

本シリーズの第4回「インターポーザに複数のシリコンダイを近接して並べる2.5次元集積化」でご説明したように、中間基板(インターポーザ)を採用する先進パッケージの寸法は拡大を続けている。その結果、2つの問題が生じた。

1つは消費電力の増加である。このことは前編で述べた。もう1つはパッケージの反り量が大きくなることだ。反りを抑えるために、パッケージの外装をリングからリッドへと変更しつつある。この変更は、熱設計に影響する。

パッケージの寸法(横軸)と消費電力および温度(縦軸、左図)、パッケージの反り量(縦軸、右図)[クリックで拡大] 出所:TSMC(IEDM 2025のショートコース(番号SC1-5)で公表された講演スライドから)

リングからリッドへの変更で放熱設計も変更へ

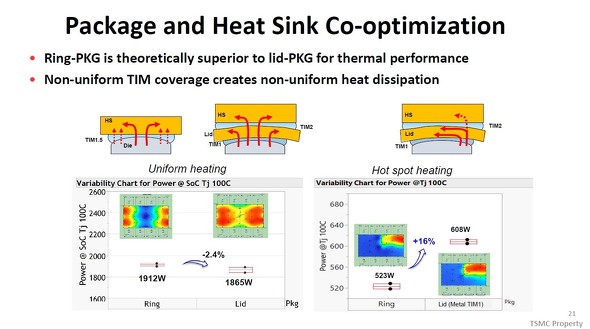

外装をリング(Ring)からリッド(Lid)に変更すると、一般的には放熱性能が低下する。リングの場合はヒートシンクとシリコンダイ(発熱源)を、1枚のTIM材料を介して接続する。リッドになるとシリコンダイとリッドを接続するTIMに加え、リッドとヒートシンクを接続するTIMが必要となる。TIMが2枚に増える。このため、原理的には熱抵抗が上昇する。言い換えると、許容可能な最大消費電力(TDP)が低下する。

そこで対策として、シリコンダイ全体から熱を均一に逃がすのではなく、発熱量の多い局所的な領域(ホットスポット)からの熱抵抗が低くなるように、TIMを改良する。こうすると外装がリッドでも、許容電力をリング外装よりも上げられる。

Copyright © ITmedia, Inc. All Rights Reserved.