AI/HPCの性能を左右する電源供給網の安定化(前編):福田昭のデバイス通信(514) TSMCが解説する最新のパッケージング技術(11)(1/2 ページ)

「IEDM 2025」におけるTSMCの講演内容を紹介するシリーズ。今回は5番目の項目「(5)Power delivery efficiency(電源供給の効率)」を前後編の2回に分けて解説する。

5番目のテーマは電源供給の効率化

2025年12月に開催された国際学会IEDMのショートコース(技術解説)で、シリコンファウンドリー最大手のTSMCが最新のパッケージング技術を説明した。講演のタイトルは「Advanced Packaging and Chiplet Technologies for AI and HPC Applications(AIおよびHPCに向けた先端パッケージング技術と先端チップレット技術)」、講演者はAdvanced Package Integration Division R&DのディレクターをつとめるJames Chen氏である。大変に参考となる内容だったので、その一部をシリーズでご紹介している。ただし講演内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演内容を筆者が適宜、補足してある。あらかじめご了承されたい。

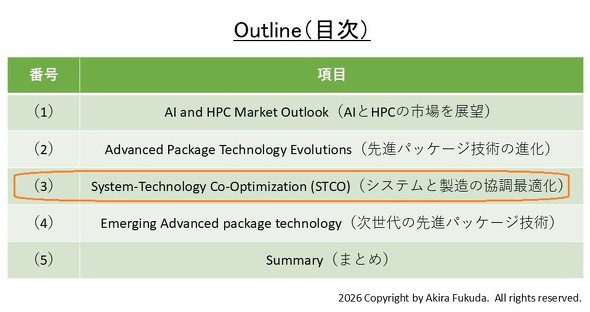

講演「Advanced Packaging and Chiplet Technologies for AI and HPC Applications(AIおよびHPCに向けた先端パッケージング技術と先端チップレット技術)」のアウトライン[クリックで拡大] 出所:TSMC(IEDM 2025のショートコース(番号SC1-5)で公表された講演スライドから)

タイトルスライドの次に示されたアウトラインは、「AI and HPC Market Outlook(AIとHPCの市場を展望)」「Advanced Package Technology Evolutions(先進パッケージ技術の進化)」「System-Technology Co-Optimization (STCO)(システムと製造の協調最適化)」「Emerging Advanced package technology(次世代の先進パッケージ技術)」「Summary(まとめ)」となっていた。

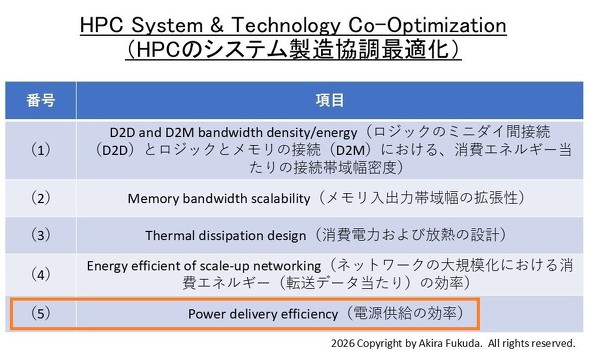

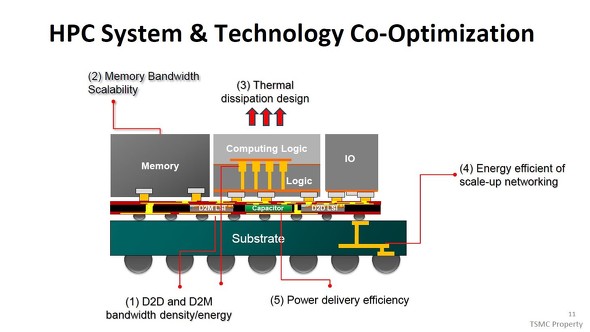

本シリーズの第5回からは、アウトラインの第3項「System-Technology Co-Optimization (STCO)(システム・製造協調最適化)」に相当する部分の説明に入った。先進パッケージ「CoWoS-L(LSI+RDL interposer)」を例に、STCOで考慮すべき5つの項目を順に説明している。

前回は4番目の項目「(4)Energy efficient of scale-up networking(ネットワークの大規模化おける消費エネルギー(転送データ当たり)の効率)」を概説した。今回は5番目の項目「(5)Power delivery efficiency(電源供給の効率)」を前後編の2回に分けてご紹介する。

STCO(システムと製造の協調最適化)で考慮すべき事柄。先進パッケージ「CoWoS-L(LSI+RDL interposer)」の例[クリックで拡大] 出所:TSMC(IEDM 2025のショートコース(番号SC1-5)で公表された講演スライドから)

抵抗損、エレクトロマイグレーション、瞬低が安定な電源供給を阻害

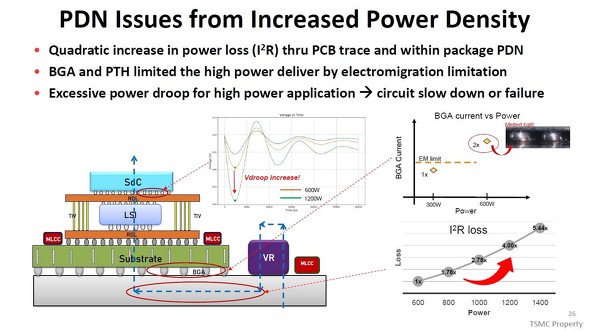

先進パッケージ「CoWoS-L」のGPU/CPUモジュールを動かすための電源は、先進パッケージを搭載したプリント回路基板の電源回路(定電圧回路(VR:Voltage Regulator))から供給される。AI/HPC向けのGPU/CPUモジュールを内蔵する先進パッケージは近年、電力密度が大きく増加しており、いくつかの課題を生じている。

電源回路(VR)からパッケージ基板までは、プリント回路基板の銅配線を通じて直流電力(電圧×電流)を供給する。電源電圧は既に限界近くまで下がっていることから、GPU/CPUモジュールの電力増大に応えるためには、電流(I)を増やすことになる。このため、プリント回路基板の電力損失(抵抗損(配線抵抗R×I×I))が増加する。同様の損失は、パッケージ内部でも発生する。

また電流密度の高まりにより、BGAパッケージの入出力端子(ボール)ではエレクトロマイグレーション(EM:ElectroMigration)が無視できなくなる。

それからGPU/CPUの負荷変動によって電源電圧の瞬時的な低下(瞬低)が発生する。瞬低を緩和するためには、GPU/CPUの動作速度が制限される恐れが出てくる。

Copyright © ITmedia, Inc. All Rights Reserved.