目指すは待機電力ゼロの夢のLSI、東北大が磁性素子利用の不揮発ロジックを実証:プロセス技術 不揮発ロジック(2/2 ページ)

もはや、従来技術の延長ではこれ以上の消費電力の削減は見込めない。今まさに、半導体チップの基本デバイスの根本的な変革が必要な時期を迎えている。

CAM/TCAMを高速化

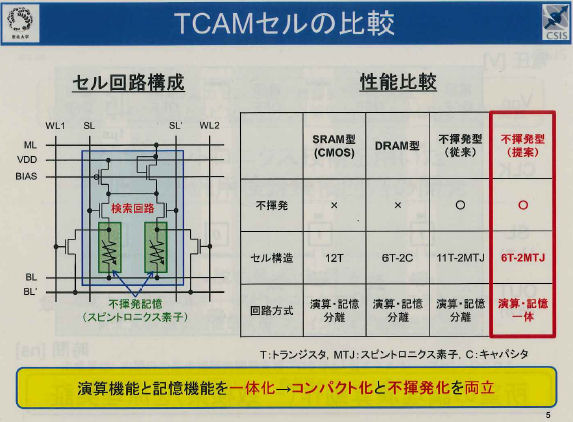

研究成果の要点は、2つある。まず1つ目の成果は、連想メモリプロセッサ(CAM)と汎用検索集積回路(TCAM)の性能改善である。

いずれも情報検索に使うロジック回路で、CAMは入力が固定された専用デバイス、TCAMは入力可変の汎用デバイスである。例えば、TCAMはネットワークルータのウイルスチェックやデータベースサーバの高速データ検索といった用途に使われている。

TCAMは、演算部とメモリ部、制御部、入出力部といった複数の要素で構成していおり、構成の観点ではシステムLSIの基本要素を全て備えている。今回、スピントロニクスを使った不揮発ロジックでTCAMを実現するとともに、現在実用化されている(CMOSロジックの)TCAMに匹敵する処理性能を実現した。「不揮発のシステムLSIの実現に道を開く成果だ」(東北大学電気通信研究所の教授である羽生貴弘氏)と語る。

羽生氏の説明によれば、「これまでは、CAM/TCAMの不揮発化と演算能力の両立ができておらず、不揮発のシステムLSIを実現する上で、CAM/TCAMの部分がネックになっていた」という。

具体的には、ロジック部とメモリ部を一体化させた「ロジック・イン・メモリ・アーキテクチャ」を採用し、記録を担う部分にスピン注入磁化反転型磁気トンネル接続(MTJ)素子を採用した。通常は分離しているロジックとメモリを1つの回路に一体化させることで、メモリ部分を不揮発化するだけで回路全体が不揮発化することになる。これまでは、逐次処理のCAM/TCAMだったが、今回、完全並列型のCAM/TCAMを実現することで、処理性能を高めた。

「現在、さまざまな機器で実用化されているTCAM(DRAM型TCAM)に匹敵する処理速度を実現した」(同氏)。しかも、世界で最も素子数が少ない完全並列型の不揮発TCAMで、回路規模は実用化されているDRAM型TCAMと同等だという。

以上の成果の一部は、2011年6月15〜17日の会期で開催されている「Symposium on VLSI Circuits」で発表する。発表論文は、「A Content Addressable Memory Using Magnetic Domain Wall Motion Cells(Session 28-3)」。NECとの共同の研究成果である。

垂直磁化型MTJ素子で10年の記録保持

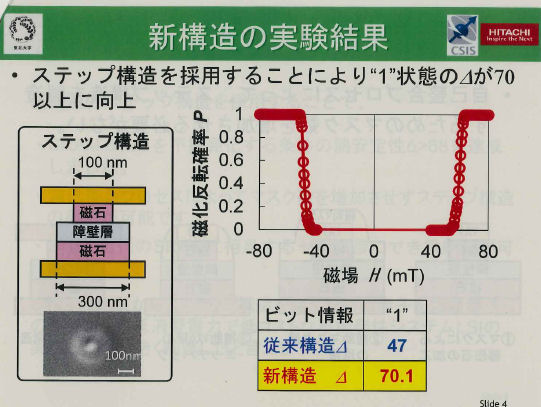

もう1つの研究成果は、不揮発化を担うMTJ素子の信頼性の改善である。大野氏の研究グループでは、2010年に垂直磁化を採用したMTJ素子を開発した。垂直磁化のMTJ素子は、面内磁化のMTJ素子に比べて、高集積化に向き、書き込み電流を下げられるといった特徴がある。

ただ一方で、垂直磁化のMTJ素子には課題があった。「1」の状態を保持しているときの記録保持能力が低いという課題だ。記録保持能力は、熱安定性に関する指標「Δ」で表現する。このΔは、不揮発性を表す指標にもなる。従来の垂直磁化のMTJ素子のΔは47。目標は10年間の記録保持に相当する68以上(64MビットのSRAMを不揮発化することを想定したとき)で、目標には遠く及ばない状況だった。

そこで今回、「ステップ構造」と呼ぶ新たな素子構造を開発した。MTJ素子は、絶縁膜を2つの強磁性体膜で挟み込んだものである。一方の強磁性体膜は磁化の方向が変わりにくく、もう一方の強磁性膜は磁化の方向が変わりやすいものを使う。前者の強磁性膜を「参照層」、後者の強磁性膜を「記録層」と呼ぶ。外部から記録層の磁化方向を変えたとき、記録層の磁化方向が参照層の磁化方向と一致すると抵抗値が低くなり、磁化方向が一致していないときは抵抗が高くなる。この抵抗の高低という2つの状態を「1」と「0」に対応させることで、情報を記録できる。

従来は、参照層と記録層の面積が同じだった構造を、参照層の面積を広くする構造にした。このステップ構造を採用することで、ビット情報が「1」のときの反発力を低減させ、Δを70以上に高めることに成功した。構造は複雑になるものの、将来的には、「自己整合プロセス」を使うことで、製造時のマスク数は増やさないで済む見通しだという。

以上の成果の一部は、2011年6月14〜16日の会期で開催されている「Symposium on VLSI Technology」で発表した。発表論文は、「CoFeB/MgO Based Perpendicular Magnetic Tunnel Junction with Stepped Structure for Symmetrizing Different Retenion Times of "0" and "1" Information(Session 11B-3)」。日立製作所との共同の研究成果である。

以上に紹介した研究は、日本学術振興会の最先端研究開発支援プログラム「省エネルギー・スピントロニクス論理集積回路の研究開発」において実施した。

課題はまだ多し

不揮発のシステムLSIの実用化に向けては、まだ幾つかの課題がある。

今後、集積規模の大きなチップを試作する。さらに、産業技術総合研究所と物質・材料研究機構、筑波大学が中核となったナノテク研究拠点である「つくばイノベーションアリーナ」の300mmウエハー採用の製造ラインを使い、MTJ素子を含む不揮発ロジックを試作する。「これより、基礎研究として完成度の高いものを見せられる。実用化の道筋をつけることにつながるだろう」(大野氏)。この他、不揮発システムLSIを設計・評価する開発ツールも用意する計画である。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

関連リンク

- 東北大学(待機電力ゼロの電子機器実現に向けて 「世界初 電子の電荷とスピンを利用した低電力システムLSIの開発・実証」について)

- 東北大学(スピントロニクス技術を用いた世界最小の待機電力フリー 汎用検索集積回路(TCAM)の実現 −磁石と半導体を組み合わせて回路の超高密度化に世界で初めて成功−)

- 東北大学(不揮発性を高めた新構造MTJ素子を世界で初めて実現 超低消費電力システムLSIの実現へ向けた、 不揮発性スピントロニクス素子の性能向上)

- 不揮発メモリ新時代(前編)

今後、メモリは全て不揮発になる。機器の機能向上につれて、増えたシステム全体の消費電力を抑えるのに、メモリの不揮発化が役立つからだ。メモリが不揮発化すれば、ほかのメリットも生じる。例えばデジタル家電を瞬時に起動できるようになる。PCの起動やシャットダウン操作が不要になる。 - 不揮発メモリ新時代(後編)

現在のDRAMやNAND型フラッシュメモリの用途に向けた次世代不揮発メモリの候補は4種類ある。FeRAM、MRAM、PRAM、ReRAMだ。ただし、どれか1つの不揮発メモリで全用途に対応することは難しそうだ。これはどの不揮発メモリにも何らかの欠点が存在するからだ。後編では不揮発メモリの用途や各不揮発メモリの性能向上策、技術動向について解説する。