「2倍の入出力帯域、5倍のDSP、60%省電力」、Alteraが描く20nm世代FPGA:プログラマブルロジック FPGA(2/2 ページ)

FPGA大手のAlteraが20nm世代の半導体プロセスで製造する次世代FPGAに向けて開発中の技術の概要を明らかにした。超高速シリアルトランシーバと、3次元実装パッケージ、可変精度のDSPブロックの3つである。製品化の時期は2013年で、製品としての具体的な仕様はあらためて発表するという。

3次元パッケージで“ヘテロジニアス”な統合を実現

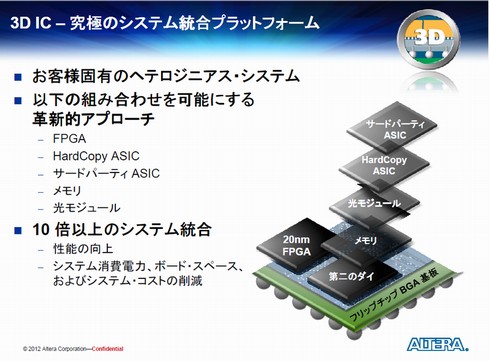

20nm世代の新技術の2つ目に掲げた3次元実装パッケージについては、シリコン材料を使った支持基板(インターポーザ)の上にFPGAなどの複数のダイを並べて実装し、単一のパッケージに封止した構造をとる。各ダイは、このシリコンインターポーザを介して信号をやりとりしたり、パッケージの端子に接続したりする仕組みだ。

複数のダイをインターポーザに実装する技術は、AlteraがFPGAチップの製造を委託している半導体ファウンダリ最大手TSMCの「CoWoS(Chip on Wafer on Substrate)」を採用する。インターポーザ用のシリコンウエハーに配線を作り込んだ後、ダイシング(切断)して個片化する前の段階で、ウエハー上の各インターポーザの領域に複数のベアチップをボンディング(接合)し、その後でダイシングするという手法だ。CoWoSに関する取り組みそのものについては、2012年の春に発表済みである。

単一のパッケージ内にFPGAのチップとともに収めることを想定するのは、DRAMやSRAMなどのメモリチップの他、ユーザーごとに異なるASICや、光トランシーバモジュールなどである。すなわち、FPGAとは異種の(ヘテロジニアスな)チップをパッケージ内で統合することを狙う。これにより、「システム統合性が10倍上も高まる。28nm世代の現行品では3次元パッケージ品を供給していないので厳密に比較することは難しいが、例えばパッケージ当たりのメモリ積載量が10倍以上に増加し、現行品ではボード上でFPGAの周辺に別に実装する必要があったメモリが不要になるといった効果が得られる」(Burich氏)とする。

GPGPUを置き換えて消費電力を1/10まで低減

Alteraが20nm世代で導入する技術のうち、3つ目の可変精度のDSP(デジタル信号処理)ブロックは、浮動小数点数演算の標準規格であるIEEE 754に準拠し、5T(テラ)FLOPSを超える演算性能を実現できるとした。これは28nm世代の現行品の5倍以上に相当し、「従来はGPGPU(General-purpose Graphics Processor Unit)チップが必要とされていた用途に使える水準だ。しかもFPGAなら、GPGPUに比べて同等性能で消費電力は1/10と小さい。具体的には、GPGPUで150W超を消費する演算を、わずか15〜20Wで実行できる」(Burich氏)という。

関連キーワード

FPGA | 20nmプロセス | アルテラ | 28nmプロセス | DSP(Digital Signal Processor) | GPGPU | TSMC | ASIC | プログラマブルロジック(エレクトロニクス)

Copyright © ITmedia, Inc. All Rights Reserved.