ハードも柔らかな「真のSDN」を実現する技術をザイリンクスが開発:これからのSDNは“Softly” Defined Network(2/2 ページ)

ザイリンクスは、SDN(Software-Defined Network)を構成するハードウェアを再構成可能なFPGAで実現する“Softly”Defined Networkを提唱している。しかし、これまでは“Softly”なSDNを構築するには大きな課題があったが、このほど「SDNet」と呼ぶ技術を開発し、FPGAによるSDNの実現に道を開いた。

設計の手間を解消

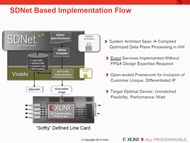

ザイリンクスは、このFPGAの抱える課題を解決する技術「SDNet」(Software Defined Specification Environment for Networking)を開発した。

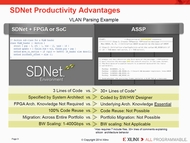

SDNetは、ひと言でいえば、高位合成ツールだ。SDNを設計するシステムアーキテクトがハードウェアに要求するレベルの記述から、HDL(ハードウェア記述言語)を自動でコンパイルし、FPGAに実装できるという。その記述量は、ASIC/ASSP設計時に記述するコード量の1/10以下とし、「HDLに精通するインプリメンテーションエンジニアの助けなしに、システムアーキテクト自らFPGAを設計できる」(コミュニケーションビジネスユニット ワイヤードマーケティングディレクターのGilles Garcia氏)とする。

こうした高位合成ツールの多くは、HDLベースで最適設計した回路に比べ、無駄が多い回路構成となる場合が多い。ただ、SDNetは、「SDNに特化して開発した技術であり、極めてオーバーヘッドは少ない。時間をかけて徹底的にHDLベースで最適化したものには劣るかもしれないが、通常のHDLベースで設計したものよりも、小さな回路で高い性能を発揮する」と言い切る。

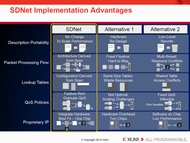

左=「SDNet」を使用した場合の設計フローイメージ / 中央=「SDNet」による設計と従来のASSP(ASIC)設計との違い / 右=SDNを実現する各デバイス(ASSP/CPU)と「SDNet」を活用したFPGAの比較 (クリックで拡大) 出典:ザイリンクス

左=「SDNet」を使用した場合の設計フローイメージ / 中央=「SDNet」による設計と従来のASSP(ASIC)設計との違い / 右=SDNを実現する各デバイス(ASSP/CPU)と「SDNet」を活用したFPGAの比較 (クリックで拡大) 出典:ザイリンクスシステムアーキテクトもFPGA設計が可能に

またSDNetを、FPGA開発環境「Vivad」と組み合わせて使用することで、既に開発済みの回路IPとの接続部の設計も自動で行える徹底して、設計の手間を削減できる。さらに、実装対象のFPGAに制限はなく、ハイエンドの「Vertexファミリ」からミドルエンドの「Kintexファミリ」、さらにはARMコア内蔵プログラマブルSoC「Zynqファミリ」から、必要な回路規模のデバイスを選択可能であり、コストも抑制できる。

現在、SDNetで生成可能な回路は、パケットプロセッシング関連回路が中心で、SDNのハードの全てをカバーしている訳ではないが、順次、柔軟性が要求される部分から対応領域を増やしていく方針。ただ現状の段階でも、「FPGAと、パケットプロセッシング用のASSPと併用した構成の機器は多い。SDNetにより、それらの機器の多くが、FPGAだけの構成に変わっていくだろう」(Garcia氏)としている。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

ザイリンクスが20nmプロセスFPGAの提供を開始、440万ロジックのVirtexも登場

ザイリンクスが20nmプロセスFPGAの提供を開始、440万ロジックのVirtexも登場

ザイリンクスは、20nmプロセスのFPGA「UltraScale」の提供を開始する。ミッドレンジの「Kintex UltraScale」ファミリとハイエンドの「Virtex UltraScale」ファミリだ。Virtex UltraScaleファミリでは、ロジックセルを440万個搭載した品種も用意する。 ザイリンクスが過去最高売上高を達成、2014年3月期

ザイリンクスが過去最高売上高を達成、2014年3月期

ザイリンクスは2014年3月期通期業績を公表し、28nmプロセス採用製品の売り上げ伸長などから過去最高売上高を記録したと明かした。 もうかる通信機器はFPGAでこそ実現できる、国内メーカーの海外展開に期待

もうかる通信機器はFPGAでこそ実現できる、国内メーカーの海外展開に期待

大手FPGAベンダーであるXilinxは、最先端の半導体製造プロセスを用いた製品開発に意欲的なことで知られている。同社は、TSMCの20nmプロセスを用いた次世代品を、2013年10〜12月期にサンプル供給する方針を既に明らかにしている。日本法人のザイリンクスで社長を務めるサム・ローガン氏に、通信機器におけるASIC/ASSPからFPGAへの置き換えの進展や、競合のAlteraが発表したIntelの14nmプロセス採用に対する見解などについて聞いた。