特集

「経験で設計すると失敗する」、ルネサスが提示する16nm FinFET SRAMの課題:メモリ/ストレージ技術(3/3 ページ)

ルネサス エレクトロニクスは、16nm FinFETプロセスを用いてSRAMを試作したと発表した。プレーナ型MOSFETを使う場合に比べて低い動作電圧で高速読み出しに成功しているが、一方でFinFETと、微細化プロセスを用いたことによる課題も増えている。

“経験で設計”すると失敗する

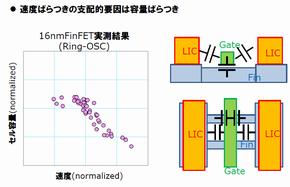

新居氏は、FinFET SRAMの懸念事項として、特性のばらつきの大きさを挙げている。同氏は「ウエハー間、ロット間、同じウエハー内のダイのばらつきなど、グローバルな(包括的な)ばらつきがやはり大きく、ここが最も気にしているところだ」と述べる。さらに「Finになって、いろいろな所に寄生容量が増えた。そのため、“本当に消費電力が下がるのか”という点についてはわれわれも心配している」(同氏)と懸念を口にする。こうしたFinに起因する容量のばらつきは28nmプロセスのプレーナ型MOSFETに比べて増大し、これが速度ばらつきにもつながっているという。

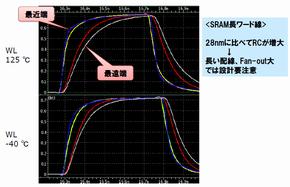

さらに、「配線抵抗が思ったよりも大きい」(新居氏)ことも課題だ。28nmに比べてR(抵抗)C(容量)が増大するので、速度が出ない、動作マージンが取れないといった問題につながると指摘している。同氏は、「今までの経験で設計すると失敗するおそれがある。きちんとRとCを計算して設計しなければならない」と続けた。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

ルネサス、16nm FinFETを用いたSRAMを開発

ルネサス、16nm FinFETを用いたSRAMを開発

ルネサス エレクトロニクスは2014年12月、16nmプロセス世代以降の車載情報機器用SoC(System on Chip)向け回路技術を開発したと発表した。 TSMC、16nm FinFETのリスク生産を開始

TSMC、16nm FinFETのリスク生産を開始

TSMCが16nmプロセスを適用したFinFETのリスク生産を開始した。開発スケジュールは予定よりも早く進んでいるようだ。今後は、AppleやQualcommなどが、新しい世代のFinFETの製造を、TSMCとSamsung Electronicsのどちらにどの程度発注していくのかが注目される。 Samsungが14nm世代のFinFETを展示、仕様は明かさず

Samsungが14nm世代のFinFETを展示、仕様は明かさず

Samsung Electronics(サムスン電子)が、ARM主催のイベントで14nm世代のFinFETプロセス技術を適用したチップを発表した。TSMCもその直前に16nm FinFETプロセスを用いたARM「Cortex-A57」の検証を行っているが、ある専門家は、16/14nm FinFETの性能については、SamsungとTSMCは互角だとみている。 動作電圧0.4V以下を実現する技術を開発、スマホの消費電力も1/10になる!?

動作電圧0.4V以下を実現する技術を開発、スマホの消費電力も1/10になる!?

新エネルギー・産業技術総合開発機構(NEDO)と超低電圧デバイス技術研究組合(LEAP)は、動作電圧が0.4V以下のロジックLSIやメモリを実現できる技術を開発した。これらの技術を使ったLSIを搭載した機器は、消費電力を1/10に低減できる可能性がある。 「SSDが壊れる」まで(前編)

「SSDが壊れる」まで(前編)

ノートPCなどのストレージとして急速に市場が拡大しているSSD(Solid State Drive)。その信頼性に対するイメージはHDDと比較されることが多いが、「平均故障間隔」と「年間故障率」の数値を単純に比較すればいいというわけではない。そこで今回は、SSDの寿命にかかわる要素を解説する。