16nm世代FPGA、ザイリンクスが「UltraScale+」ファミリを発表:プログラマブルロジック FPGA(3/3 ページ)

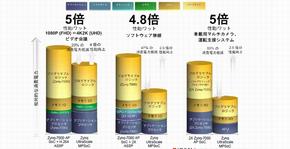

ザイリンクスは、16nmプロセス技術を用いた次世代FPGA「UltraScale+」ファミリを発表した。従来の28nmプロセスFPGA/SoCに比べて、消費電力当たり2〜5倍のシステム性能を実現することが可能となる。

ハイレベルの異種マルチプロセッシングを実現

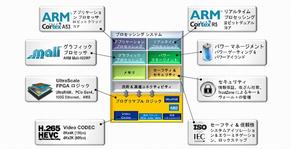

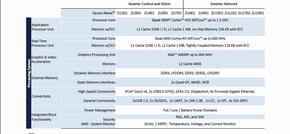

Zynq 16nm UltraScale+MPSoCは、FPGA技術に加えて、ヘテロジニアスなマルチプロセッシング機能を備えている。プロセッシングブロックには、TrustZoneをサポートする64ビットクアッドコア「ARM Cortex-A53プロセッサ」と、Lock-Step機能などを備えたリアルタイム処理向けの32ビットデュアルコア「ARM Cortex-R5プロセッサ」を搭載している。

また、グラフィックス処理を高速に実行するため、プロセッシングブロックに専用グラフィックスプロセッサ「ARM Mali-400MP」を搭載した。プログラマブルロジックブロックには、ビデオ圧縮/解凍処理を実行する専用の「H.264ビデオコーディックユニット」をハードウェアIPとして内蔵した製品も用意している。CPUコアを含めこれらの演算ユニットをタスクごとに使いこなすことで、消費電力当たりのシステム性能は、従来製品に比べて最大5倍に高めることができるという。また、入出力インタフェースとして、DisplayPortやMIPI、HDMIを備えている。

2015年第4四半期より出荷開始

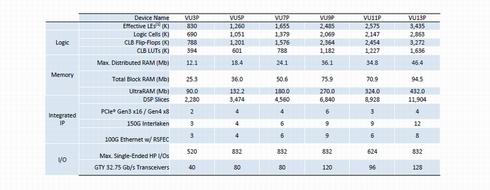

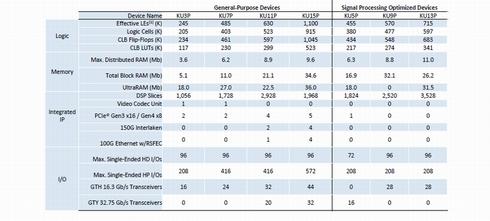

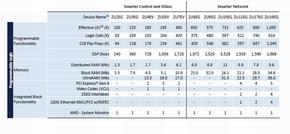

今回発表したUltraScale+ファミリは、Virtex UltraScale+で6製品、Kintex UltraScale+で7製品、Zynq UltraScale+MPSoCで11製品を用意した。最初のテープアウトとデザインツールのアーリーアクセスプログラムは、2015年第2四半期(4〜6月)を予定している。製品出荷は2015年第4四半期(10〜12月)となる見通しだ。

16nmプロセス技術を用いた次世代FPGA「UltraScale+」ファミリは、LTE Advancedや5世代ワイヤレス通信、テラビットワイヤード通信、ADAS(先進運転支援システム)、産業用IoTなどの用途に向ける。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

ザイリンクスが400Gb イーサネットの動作デモを公開――20nmFPGAで

ザイリンクスが400Gb イーサネットの動作デモを公開――20nmFPGAで

Xilinx(ザイリンクス)は2014年11月、エンジニアリングサンプル(ES)出荷段階にある20nmプロセスを用いたFPGA「Virtex UltraScaleファミリ XCVU095」を使用した400Gビット イーサネットの動作デモを公開した。 ザイリンクス優位は、20nm/16nm世代でも揺るがない

ザイリンクス優位は、20nm/16nm世代でも揺るがない

ザイリンクス日本法人は、現行の主力28nmプロセス採用FPGAの受注が好調だという。同社社長を務めるサム・ローガン氏に好調の理由や、今後、投入を本格化させる20nmプロセス採用FPGA製品のビジネス展望などを聞いた。 ザイリンクスが20nmプロセスFPGAの提供を開始、440万ロジックのVirtexも登場

ザイリンクスが20nmプロセスFPGAの提供を開始、440万ロジックのVirtexも登場

ザイリンクスは、20nmプロセスのFPGA「UltraScale」の提供を開始する。ミッドレンジの「Kintex UltraScale」ファミリとハイエンドの「Virtex UltraScale」ファミリだ。Virtex UltraScaleファミリでは、ロジックセルを440万個搭載した品種も用意する。 ザイリンクスが過去最高売上高を達成、2014年3月期

ザイリンクスが過去最高売上高を達成、2014年3月期

ザイリンクスは2014年3月期通期業績を公表し、28nmプロセス採用製品の売り上げ伸長などから過去最高売上高を記録したと明かした。 ザイリンクス、20nmプロセスFPGAをテープアウト――製品戦略反映し呼称も「8」ではなく「UltraScale」

ザイリンクス、20nmプロセスFPGAをテープアウト――製品戦略反映し呼称も「8」ではなく「UltraScale」

ザイリンクスは、20nmプロセス技術を用いたFPGAのテープアウト(設計完了)を発表した。同時に、20nmプロセス採用FPGAなどに適用する新世代アーキテクチャ「UltraScale」の概要も公表した。新プロセス、新アーキテクチャを採用した製品の出荷は2013年10〜12月を予定している。